AGB Programming Manual

Rendering Functions

©1999 - 2001 Nintendo of America Inc.

50

D.C.N. AGB-06-0001-002B4

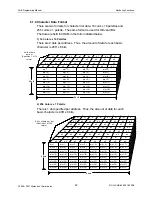

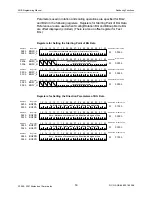

Parameters used in rotation and scaling operations are specified for BG2

and BG3 in the following registers. Registers for Starting Point of BG Data

Reference are also used when Scaling/Rotation BG and Bitmap Mode BG

are offset displayed (scrolled). (There is also an offset register for Text

BG.)

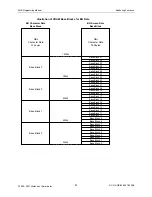

Registers for Setting the Starting Point of BG Data

15

14 13

12

11 10

09

08 07

06

05 04

03

02 01

00

BG2X_L

BG3X_L

028h

038h

0000h

W

Address

Register

AttributesInitial Value

X-coordinate of reference starting point (rotation/scaling results)

15

14 13

12

11 10

09

08 07

06

05 04

03

02 01

00

BG2X_H

BG3X_H

02Ah

03Ah

0000h

W

Address

Register

AttributesInitial Value

15

14 13

12

11 10

09

08 07

06

05 04

03

02 01

00

BG2Y_L

BG3Y_L

02Ch

03Ch

0000h

W

Address

Register

Attributes Initial Value

15

14 13

12

11 10

09

08 07

06

05 04

03

02 01

00

BG2Y_H

BG3Y_H

02Eh

03Eh

0000h

W

Address

Register

AttributesInitial Value

Y-coordinate of reference starting point

(rotation/scaling results)

Y-coordinate of reference starting point (rotation/scaling results)

X-coordinate of reference starting point

(rotation/scaling results)

Registers for Setting the Direction Parameters of BG Data

15

14 13

12

11 10

09

08 07

06

05 04

03

02 01

00

BG2PA

BG3PA

020h

030h

0100h

W

Address

Register

Attributes Initial Value

dx: distance of movement in x direction along same line

15

14 13

12

11 10

09

08 07

06

05 04

03

02 01

00

BG2PB

BG3PB

022h

032h

0000h

W

Address

Register

dmx: distance of movement in x direction along next line

15

14 13

12

11 10

09

08 07

06

05 04

03

02 01

00

BG2PC

BG3PC

024h

034h

0000h

W

Address

Register

dy: distance of movement in y direction along same line

15

14 13

12

11 10

09

08 07

06

05 04

03

02 01

00

BG2PD

BG3PD

026h

036h

0100h

W

Address

Register

dmy: distance of movement in y direction along next line

Attributes Initial Value

Attributes Initial Value

Attributes Initial Value