PRELIMINARY ISD1700 SERIES

Publication Release Date: Nov 6, 2008

- 57 -

Revision 1.31

The additional command enhances the functionality and performance of the device in order to fulfill

extra features and requirements that the designers may wish.

11.5.1 EXTCLK (0x4A)

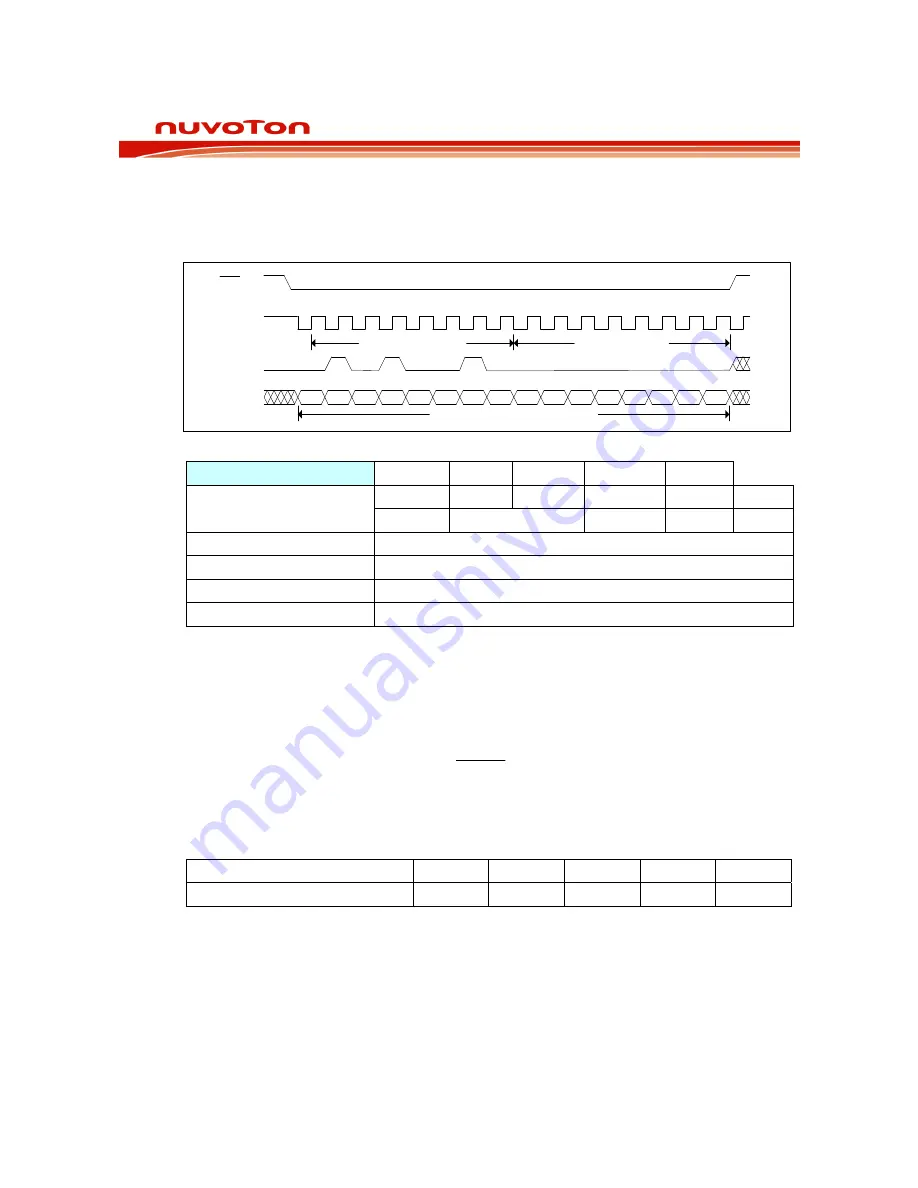

B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15

SCLK

MOSI

MISO

SS

Data Byte 1

Command (4Ah)

LSB

MSB

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

MSB LSB

Status Register 0 : Bytes #1 & #2

EXTCLK

Opcode 0x4A 0x00 Interrupt No

Byte Sequence:

MOSI

0x4A

0x00

MISO SR0

Description:

Enable or disable the external clock mode

State before Execution

Idle

State after Execution

Idle

Registers Affected

None

The EXTCLK command toggles the enable and disable of the external clock (XCLK) mode on the

device. When XCLK mode is activated, the internal oscillator of the device is disabled. Instead, an

external clock is required to apply to the Rosc pin and the external resistor at Rosc pin must be

removed. When XCLK mode is disabled, then the external clock signal must be disconnected from

Rosc pin and an external resistor must be connected back, so that the device runs from its internal

clock accordingly. This mode is very useful for synchronization of the I1700 device with an external

component, such as microcontroller, when precision timing is essential. An active XCLK state can

also be reset by RESET command or

RESET

pin. Hence, the device will operate via its internal

oscillator, provided that the external resistor is hooked up to the Rosc pin.

The frequencies of the required external clock with respect to the various sampling frequencies are

listed in the below table, but duty cycle is not important since it will be taken care internally by the

device.

Sampling Freq. [kHz]

12

8

6.4

5.3

4

External Clock Freq. [MHz]

3.072 2.048 1.638 1.356 1.024