ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 127 -

Revision 2.4

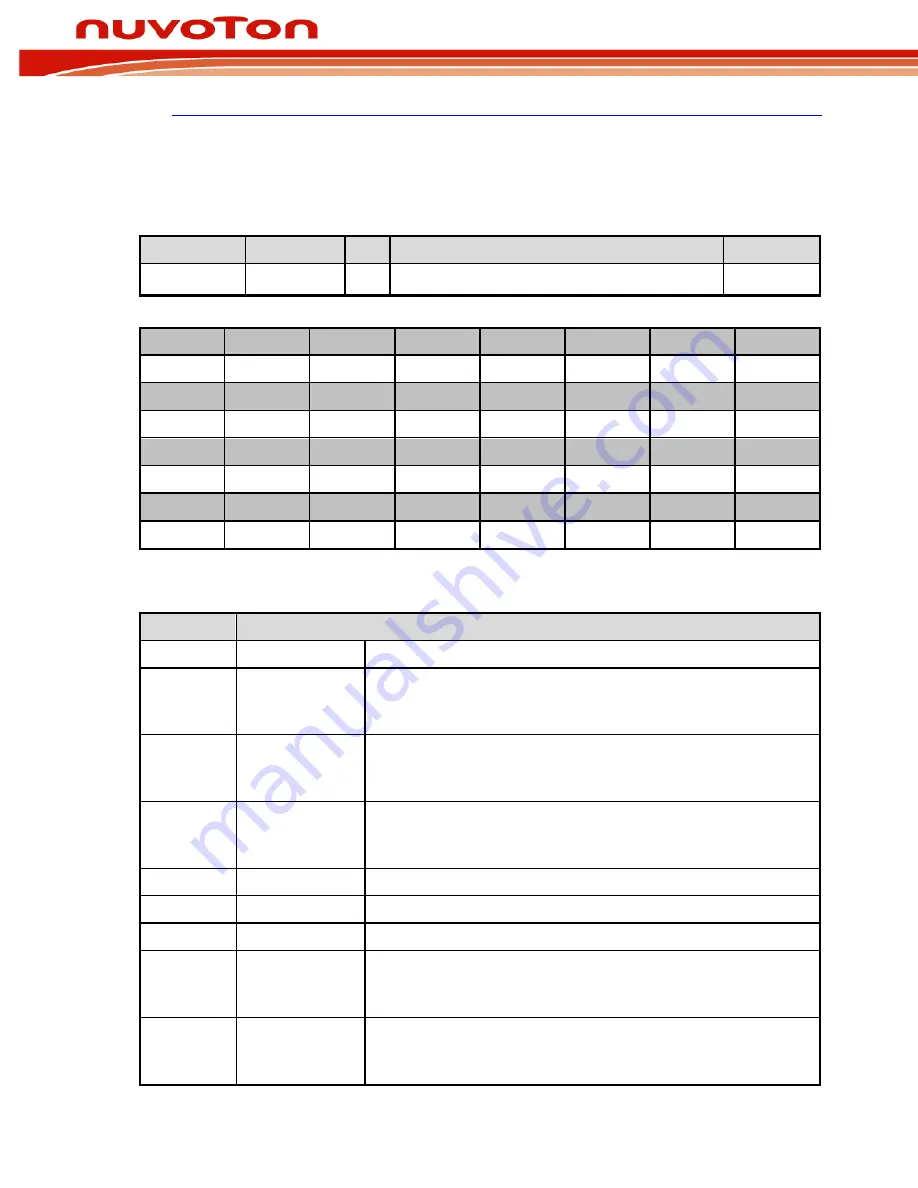

Sleep Clock Enable Control Register

(

CLK_SLEEPCTL

)

These register bits are used to enable/disable clocks during sleep mode. It works in conjunction with

CLK_AHBCLK and CLK_APBCLK0 clock register to determine whether a clock source remains active

during CPU Sleep mode. For a clock to be active in Sleep mode, the appropriate clock must be enabled

in the CLK_AHBCLK or CLK_APBCLK0 register and the bit must also be enabled in the

CLK_SLEEPCTL register. In other words, to disable a clock in Sleep mode, write ‘0’ to the appropriate

bit in CLK_SLEEPCTL.

Register

Offset

R/W

Description

Reset Value

CLK_SLEEPCTL

0x20 R/W

Sleep Clock Source Select Register

0xFFFF_FFFF

31

30

29

28

27

26

25

24

Reserved

ANACKEN

I2SCKEN

SDADCCKEN

Reserved

Reserved

Reserved

Reserved

23

22

21

20

19

18

17

16

Reserved

Reserved

PWM0CH23C

KEN

PWM0CH01C

KEN

Reserved

BQALCKEN SARADCCKE

N

UART0CKEN

15

14

13

12

11

10

9

8

UART1CKEN

Reserved

DPWMCKEN

SPI0CKEN

SPI1CKEN

Reserved

Reserved

I2C0CKEN

7

6

5

4

3

2

1

0

TMR1CKEN

TMR0CKEN

RTCCKEN

WDTCKEN

Reserved

ISPCKEN

PDMACKEN

HCLKCKEN

Table 5-45 Sleep Clock Enable Control Register (CLK_SLEEPCTL, address 0x5000_0220).

Bits

Description

[31]

Reserved

[30]

ANACKEN

Analog Block Sleep Clock Enable Control

0=Disable.

1=Enable.

[29]

I2SCKEN

I2S Sleep Clock Enable Control

0=Disable.

1=Enable.

[28]

SDADCCKEN

Delta-Sigma Analog-digital-converter (ADC) Sleep Clock Enable Control

0=Disable.

1=Enable.

[27]

Reserved

[26]

Reserved

[25:22]

Reserved

[21]

PWM0CH23CKEN

PWM0CH2 and PWM0CH3 Block Sleep Clock Enable Control

0=Disable.

1=Enable.

[20]

PWM0CH01CKEN

PWM0CH0 and PWM0CH1 Block Sleep Clock Enable Control

0=Disable.

1=Enable.