ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 187 -

Revision 2.4

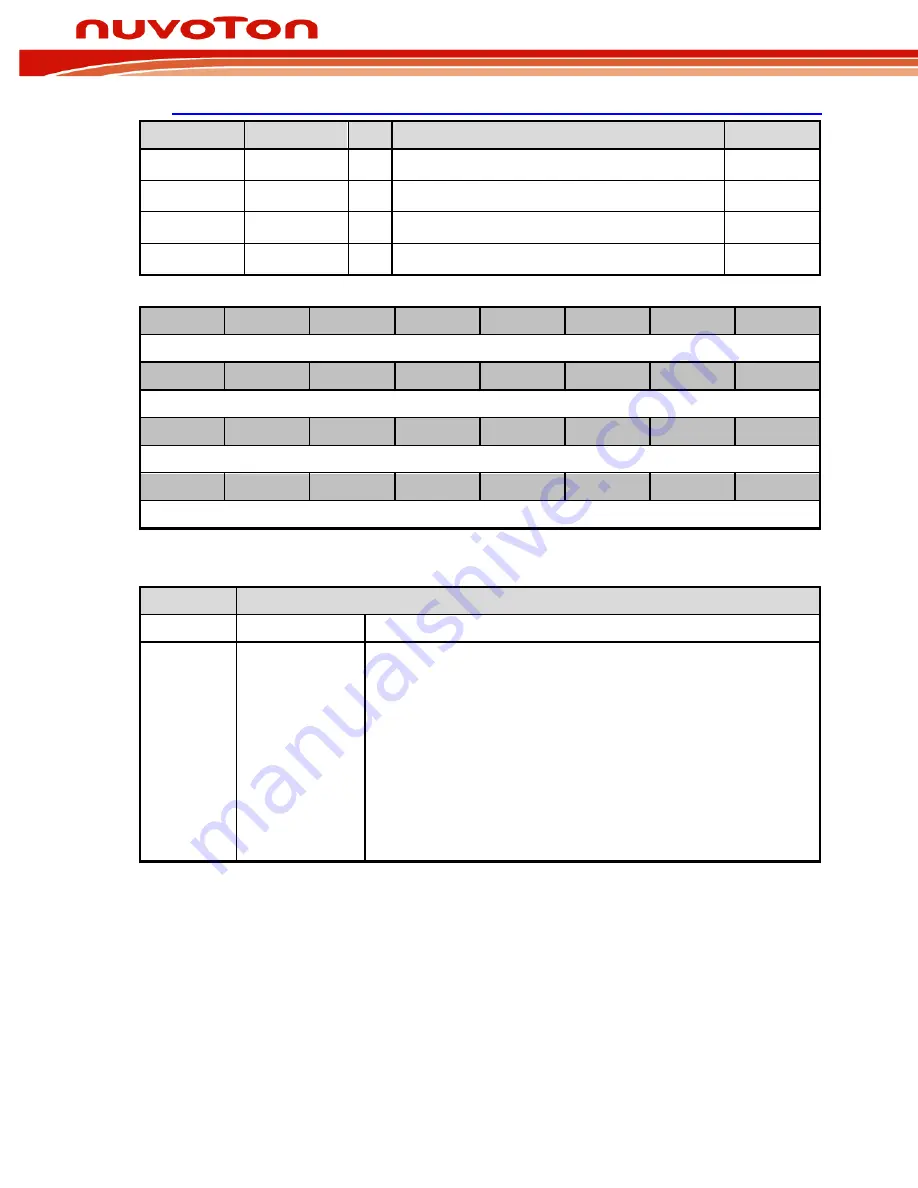

PWM Counter Register 1-0 (PWM_PERIOD1-0)

Register

Offset

R/W

Description

Reset Value

PWM_PERIOD0

0x00C R/W

PWM Counter Register 0

0x0000_0000

PWM_PERIOD1

0x018 R/W

PWM Counter Register 1

0x0000_0000

PWM_PERIOD2

0x024 R/W

PWM Counter Register 2

0x0000_0000

PWM_PERIOD3

0x030 R/W

PWM Counter Register 3

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

PERIOD [15:8]

7

6

5

4

3

2

1

0

PERIOD [7:0]

Table 5-65 PWM Counter Register (PWM_PERIODx, address 0x4C*x).

Bits

Description

[31:16]

Reserved

Reserved.

[15:0]

PERIOD

PWM Counter/Timer Reload Value

PERIOD determines the PWM period.

PWM frequency = PWM0CHx_CLK/(p1)*(clock divider)/(1);.

Duty ratio = (CMP+1)/(1).

CMP > = PERIOD: PWM output is always high.

CMP < PERIOD: PWM low width = (PERIOD-CMP) unit; PWM high width =

(CMP+1) unit.

CMP = 0: PWM low width = (PERIOD) unit; PWM high width = 1 unit.

(Unit = one PWM clock cycle).

Note:

Any write to PERIOD will take effect in next PWM cycle.