ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 280 -

Revision 2.4

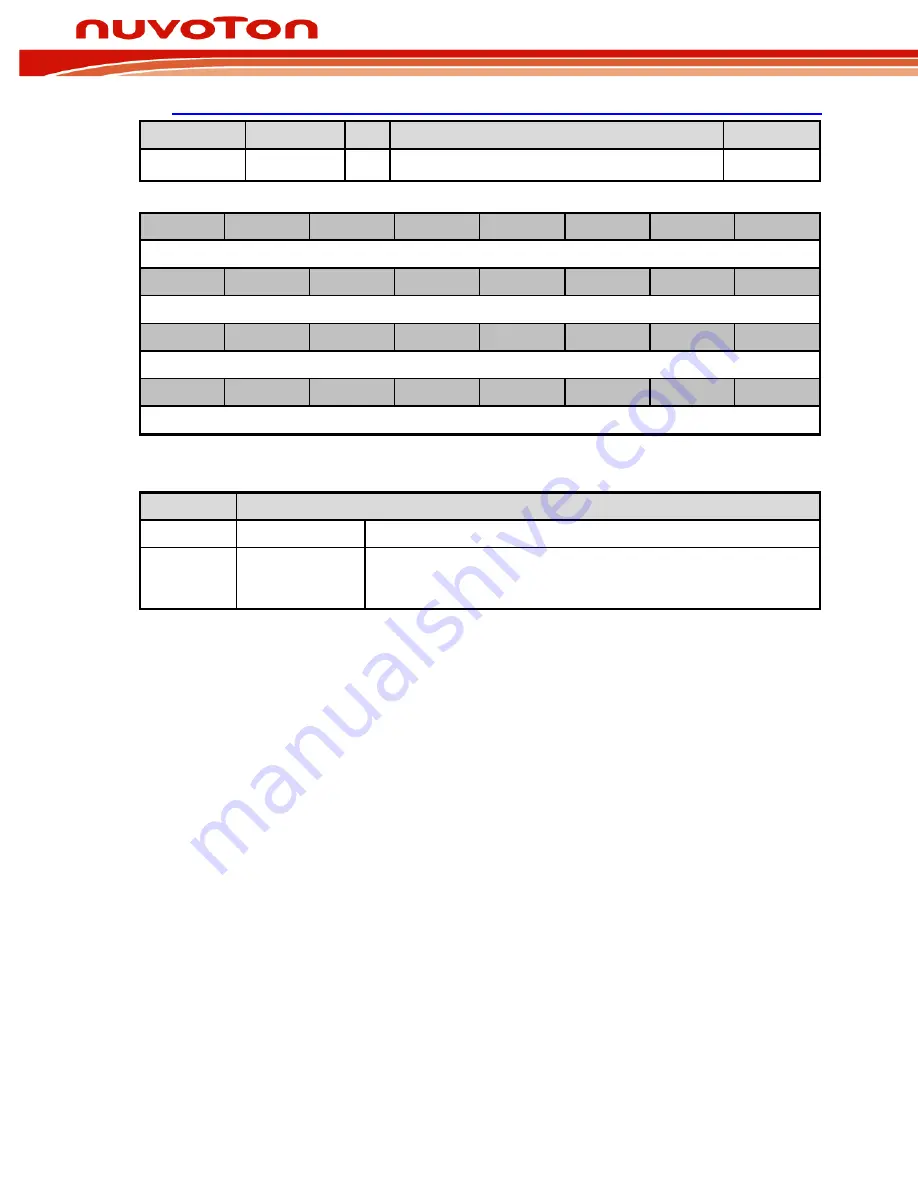

Timer Data Register (TIMERn_CNT)

Register

Offset

R/W

Description

Reset Value

TMRn_CNT

0x0C R/W

Timer Data Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

CNT[23:16]

15

14

13

12

11

10

9

8

CNT[15:8]

7

6

5

4

3

2

1

0

CNT[7:0]

Table 5-113 Timer Data Register (TIMERx_CNT, address 0x400 x *0x20).

Bits

Description

[31:24]

Reserved

Reserved.

[23:0]

CNT

Timer Data Register

When TIMERx_CTL.CNTDATEN is set to 1, the internal 24-bit timer up-counter

value will be latched into CNT. User can read this register for the up-counter value.