ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 306 -

Revision 2.4

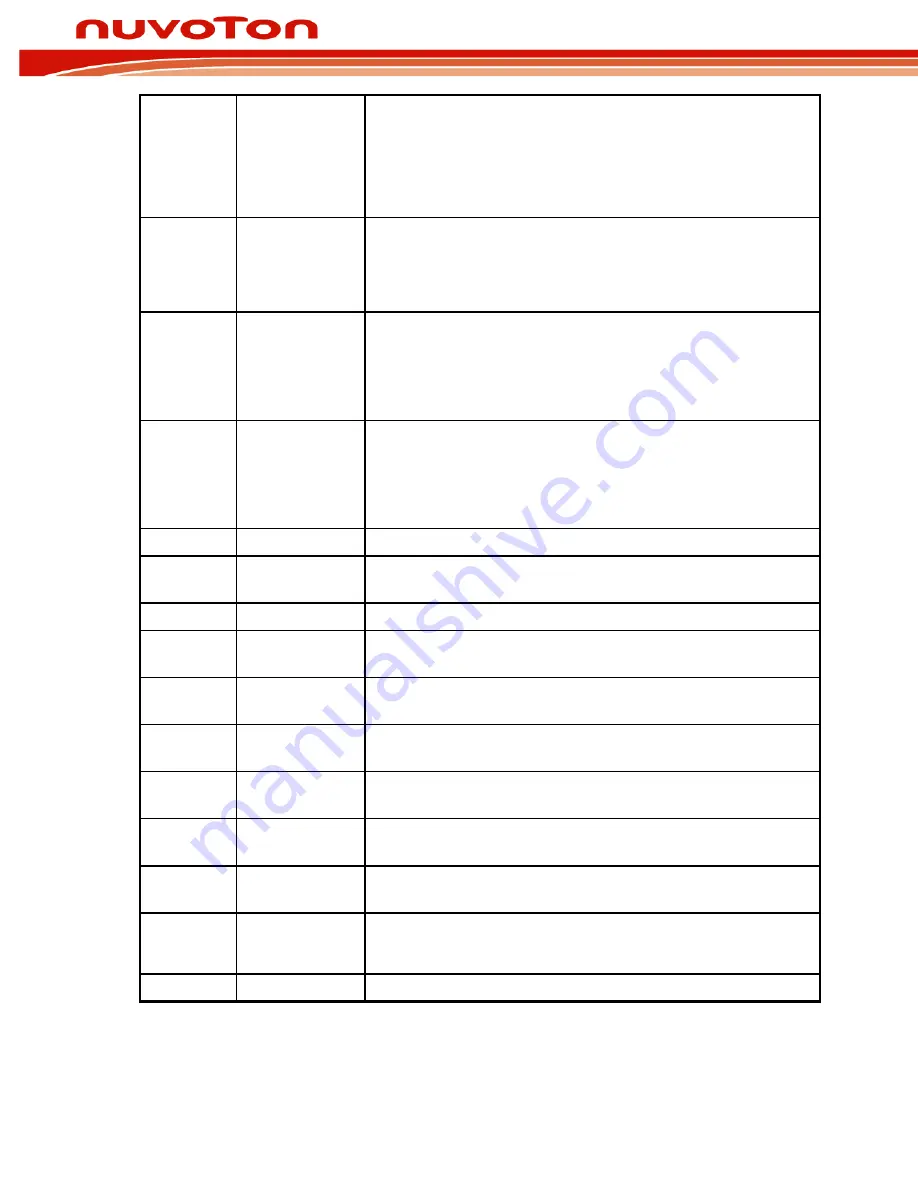

[21]

DBERRIF

DMA MODE Buffer Error Interrupt Flag (Read Only)

This bit is set when either the Tx or Rx FIFO overflows (UART_FIFOSTS.TXOVIF or

UART_FIFOSTS.RXOVIF is set). When BUFERRIF is set, the serial transfer may be

corrupted. If UART_INTEN.BUFERRIEN is enabled a CPU interrupt request will be

generated.

NOTE: This bit is cleared when both UART_FIFOSTS.TXOVIF and

UART_FIFOSTS.RXOVIF are cleared.

[20]

DRXTOIF

DMA MODE Time Out Interrupt Flag (Read Only)

This bit is set when the Rx FIFO is not empty and no activity occurs in the Rx FIFO

and the time out counter equal to TOIC. If UART_INTEN.TOUT_IEN is enabled a

CPU interrupt request will be generated.

NOTE: This bit is read only and user can read FIFO to clear it.

[19]

DMODEMIF

DMA MODE MODEM Interrupt Flag (Read Only)

This bit is set when the CTS pin has changed state

(UART_MODEMSTS.CTSDETF=1). If UART_INTEN.MODEMIEN is enabled, a CPU

interrupt request will be generated.

NOTE: This bit is read only and reset when bit UART_MODEMSTS.CTSDETF is

cleared by a write 1.

[18]

DRLSIF

DMA MODE Receive Line Status Interrupt Flag (Read Only)

This bit is set when the Rx receive data has a parity, framing or break error (at least

one of, UART_FIFOSTS.BIF, UART_FIFOSTS.FEF and UART_FIFOSTS.PEF, is

set). If UART_INTEN.RLSIEN is enabled, the RLS interrupt will be generated.

NOTE: This bit is read only and reset to 0 when all bits of BIF, FEF and PEF are

cleared.

[17:16]

Reserved

Reserved.

[15]

LININT

LIN Bus Rx Break Field Detected Interrupt Indicator to Interrupt Controller

Logical AND of UART_INTEN.LINIEN and LINIF.

[14]

Reserved

Reserved.

[13]

BUFERRINT

Buffer Error Interrupt Indicator to Interrupt Controller

Logical AND of UART_INTEN.BUFERRIEN and BUFERRIF.

[12]

RXTOINT

Time Out Interrupt Indicator to Interrupt Controller

Logical AND of UART_INTEN.RXTOIEN and RXTOIF.

[11]

MODEMINT

MODEM Status Interrupt Indicator to Interrupt

Logical AND of UART_INTEN.MODEMIEN and MODENIF.

[10]

RLSINT

Receive Line Status Interrupt Indicator to Interrupt Controller

Logical AND of UART_INTEN.RLSIEN and RLSIF.

[9]

THERINT

Transmit Holding Register Empty Interrupt Indicator to Interrupt Controller

Logical AND of UART_INTEN.THREIEN and THREIF.

[8]

RDAINT

Receive Data Available Interrupt Indicator to Interrupt Controller

Logical AND of UART_INTEN.RDAIEN and RDAIF.

[7]

LINIF

LIN Bus Rx Break Field Detected Flag

This bit is set when LIN controller detects a break field. This bit is cleared by writing

a 1.

[6]

Reserved

Reserved.