ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 325 -

Revision 2.4

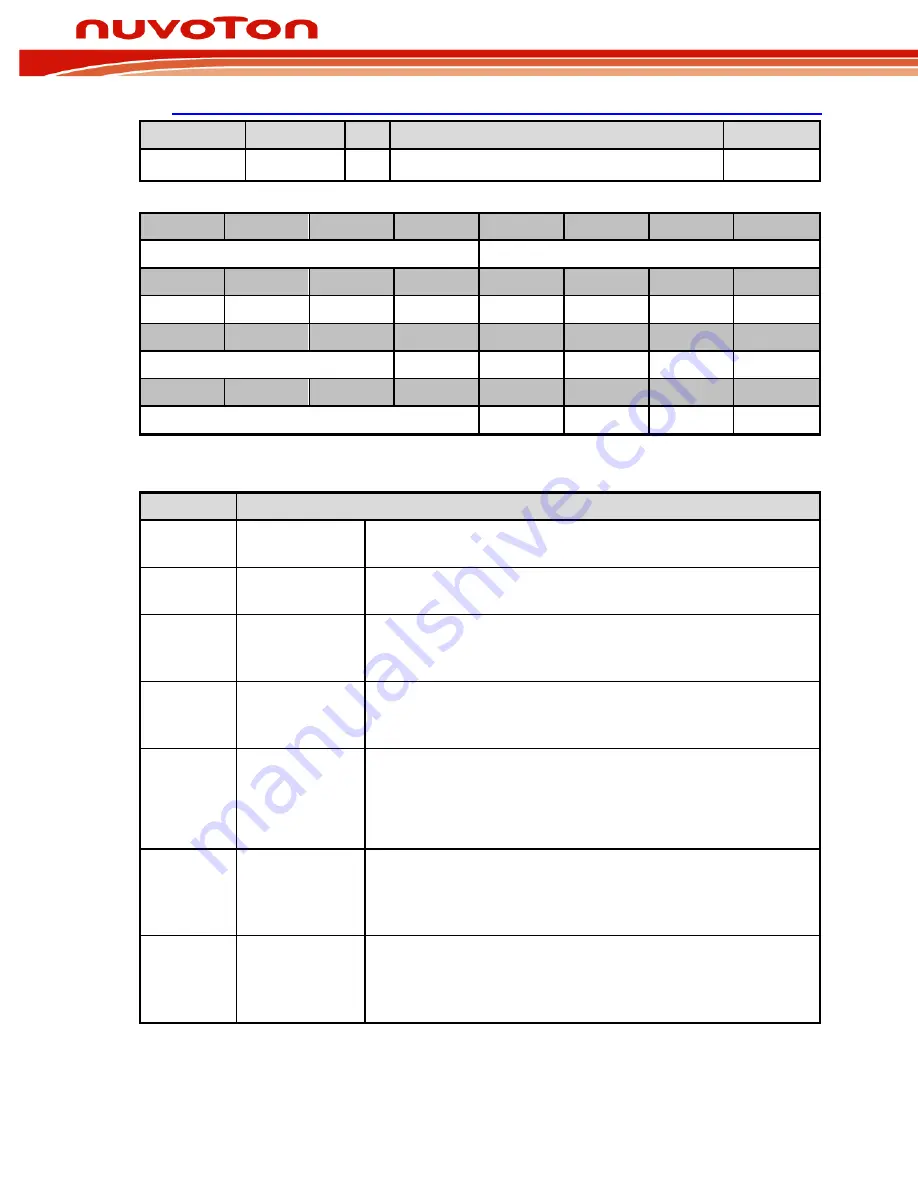

I2S Status Register (I2S_STATUS)

Register

Offset

R/W

Description

Reset Value

I2S_STATUS

0x0C

R/W

I2S Status Register

0x0014_1100

31

30

29

28

27

26

25

24

TXCNT

RXCNT

23

22

21

20

19

18

17

16

LZCIF

RZCIF

TXBUSY

TXEMPTY

TXFULL

TXTHIF

TXOVIF

TXUDIF

15

14

13

12

11

10

9

8

Reserved

RXEMPTY

RXFULL

RXTHIF

RXOVIF

RXUDIF

7

6

5

4

3

2

1

0

Reserved

RIGHT

TXIF

RXIF

I2SIF

Table 5-135 I2S Status Register (I2S_STATUS, address 0x400A_000C)

Bits

Description

[31:28]

TXCNT

Transmit FIFO Level (Read Only)

TXCNT = number of words in transmit FIFO.

[27:24]

RXCNT

Receive FIFO Level (Read Only)

RXCNT = number of words in receive FIFO.

[23]

LZCIF

Left Channel Zero Cross Flag (Write ‘1’ to Clear, or Clear LZCEN)

0 = No zero cross detected.

1 = Left channel zero cross is detected.

[22]

RZCIF

Right Channel Zero Cross Flag (Write ‘1’ to Clear, or Clear RZCEN)

0 = No zero cross.

1 = Right channel zero cross is detected.

[21]

TXBUSY

Transmit Busy (Read Only)

This bit is cleared when all data in transmit FIFO and Tx shift register is shifted out. It

is set when first data is loaded to Tx shift register.

0 = Transmit shift register is empty.

1 = Transmit shift register is busy.

[20]

TXEMPTY

Transmit FIFO Empty (Read Only)

This is set when transmit FIFO is empty.

0 = Not empty.

1 = Empty.

[19]

TXFULL

Transmit FIFO Full (Read Only)

This bit is set when transmit FIFO is full.

0 = Not full.

1 = Full.