ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 37 -

Revision 2.4

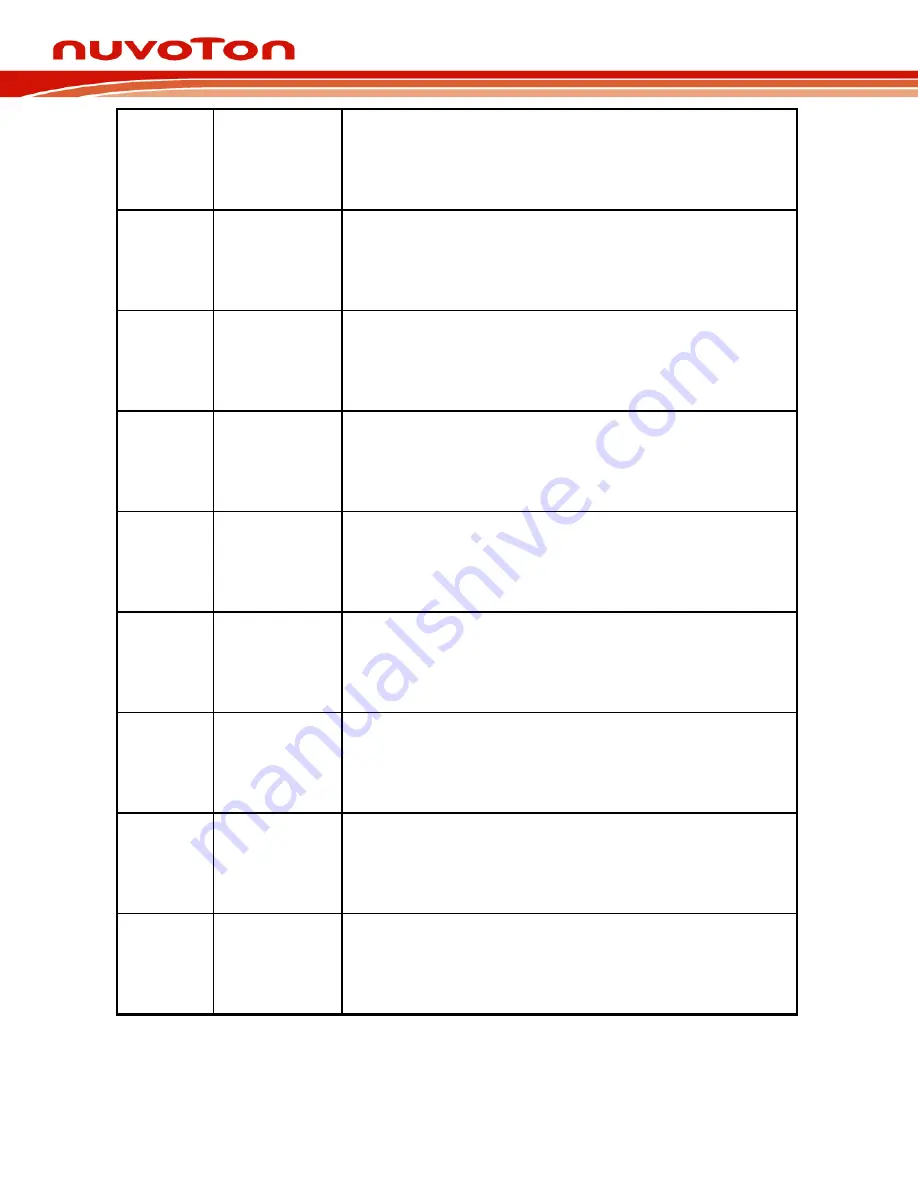

[26]

SSGPBG1

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOB 7/6/5/4

input Schmitt Trigger enabled.

0 = GPIOB 7/6/5/4

input CMOS enabled.

[25]

HSSGPBG0

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOB 3/2/1/0 Output high slew rate.

0 = GPIOB 3/2/1/0 Output low slew rate

.

[24]

SSGPBG0

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOB 3/2/1/0

input Schmitt Trigger enabled.

0 = GPIOB 3/2/1/0

input CMOS enabled.

[23]

HSSGPAG3

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOA 15/14/13/12 Output high slew rate.

0 = GPIOA 15/14/13/12 Output low slew rate

.

[22]

SSGPAG3

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOA 15/14/13/12

input Schmitt Trigger enabled.

0 = GPIOA 15/14/13/12

input CMOS enabled.

[21]

HSSGPAG2

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOA 11/10/9/8 Output high slew rate.

0 = GPIOA 11/10/9/8 Output low slew rate

.

[20]

SSGPAG2

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOA 11/10/9/8

input Schmitt Trigger enabled.

0 = GPIOA 11/10/9/8

input CMOS enabled.

[19]

HSSGPAG1

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOA 7/6/5/4 Output high slew rate.

0 = GPIOA 7/6/5/4 Output low slew rate

.

[18]

SSGPAG1

this Register Controls Whether the GPIO Input Buffer Schmitt Trigger Is

Enabled and Whether High or Low Slew Rate Is Selected for Output Dr.

Each bit controls a group of four GPIO pins

1 = GPIOA 7/6/5/4

input Schmitt Trigger enabled.

0 = GPIOA 7/6/5/4

input CMOS enabled.