ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 393 -

Revision 2.4

Register

Offset

R/W

Description

Reset Value

BS_BANDGPLDO

S0x24 R/W

Bridge Sense Bandgap and LDO Control Register

0x0000_400e

BS_INSTRAMP

S0x28 R/W

Bridge Sense Instrumentation Amplifer Control Register

0x000c_0c00

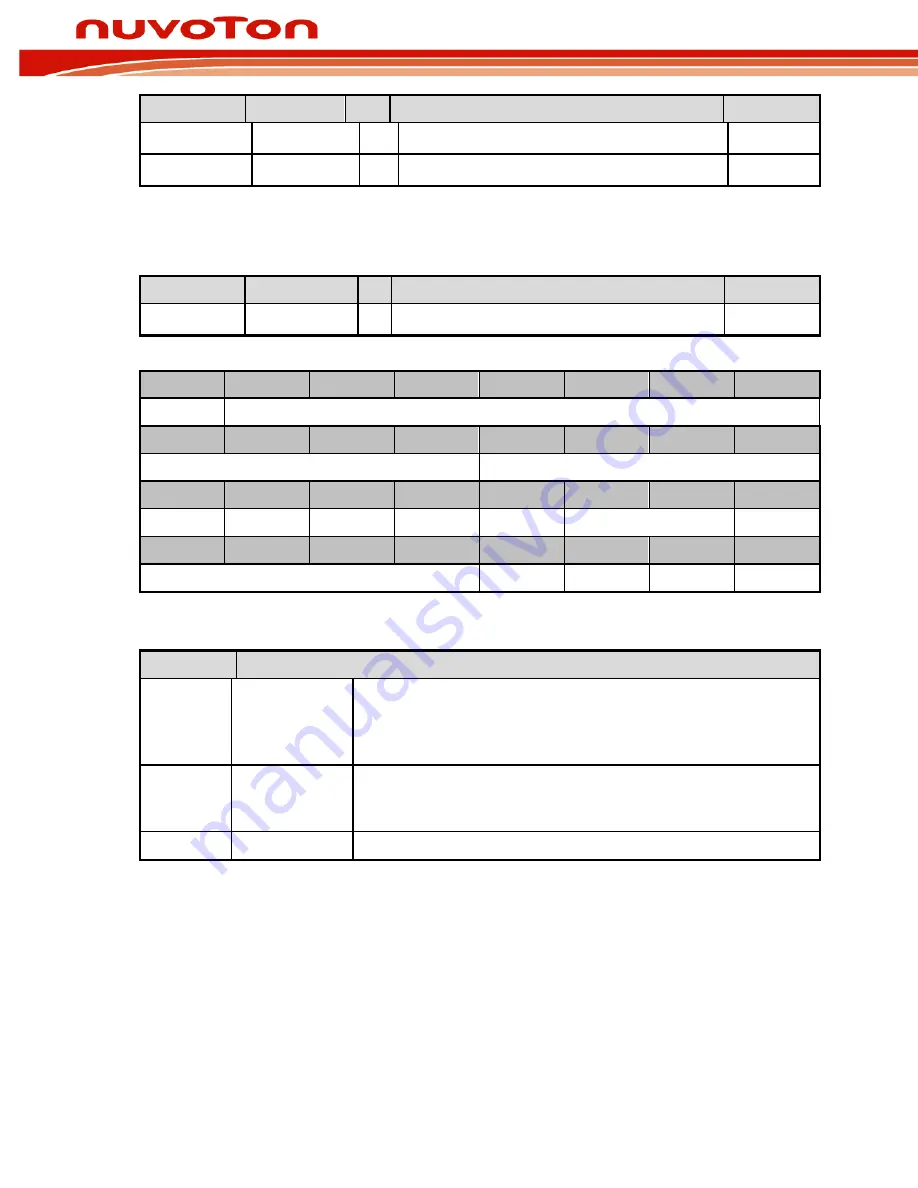

7.2.6

Register Description

Bridge Sense Bandgap and LDO Control Register(BS_BANDGP_LDO)

Register

Offset

R/W Description

Reset Value

BS_BANDGPLDO

BS_BA+0x0

R/W Bridge Sense Bandgap and LDO Control Register

0x0000_400e

31

30

29

28

27

26

25

24

CLKEN

CLKDIV

23

22

21

20

19

18

17

16

Reserved

LDOSET

15

14

13

12

11

10

9

8

Reserved

DIVEN

DISCHRG

LDOEN

Reserved

BGCCDIVF

BCHOPPH

7

6

5

4

3

2

1

0

BTRIM

BCHOPLFEN

BCHOPEN

BFLTCHRG

BGEN

Bits

Description

[31]

CLKEN

Bridge Sense clock enable for 400KHz, 200KHz and 160Hz

0 = disable

1 = enable

[30:24]

CLKDIV

Bridge Sense clock divider for 400KHz

ADC_CLK /(2*400K)

[23:20]

Reserved

Reserved