ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 398 -

Revision 2.4

7.3

Audio Class D Speaker Driver (DPWM)

7.3.1

Functional Description

The ISD91200 includes a differential Class D (PWM) speaker driver capable of delivering 0.5W into an

8

Ω

load at 5V supply voltage. The driver works by up-sampling and modulating a PCM input to

differentially drive the SPK+ and SPK- pins. The speaker driver operates from its own independent

supply VCCSPK and VSSSPK. This supply should be well decoupled as peak currents from speaker

driver are large.

7.3.2

Features

Differential Audio PWM Output (DPWM).

Direct connection of speaker

0.5W drive capability into 8Ω load at 5.5V.

Configurable up-sampling to support sample rates from 8~48kHz.

Programmable volume control from -108dB to +36dB in 0.5 dB step.

Programmable biquad filter to support multiple sample rates from 8~48kHz.

PDMA data channel for streaming of PCM audio data.

7.3.3

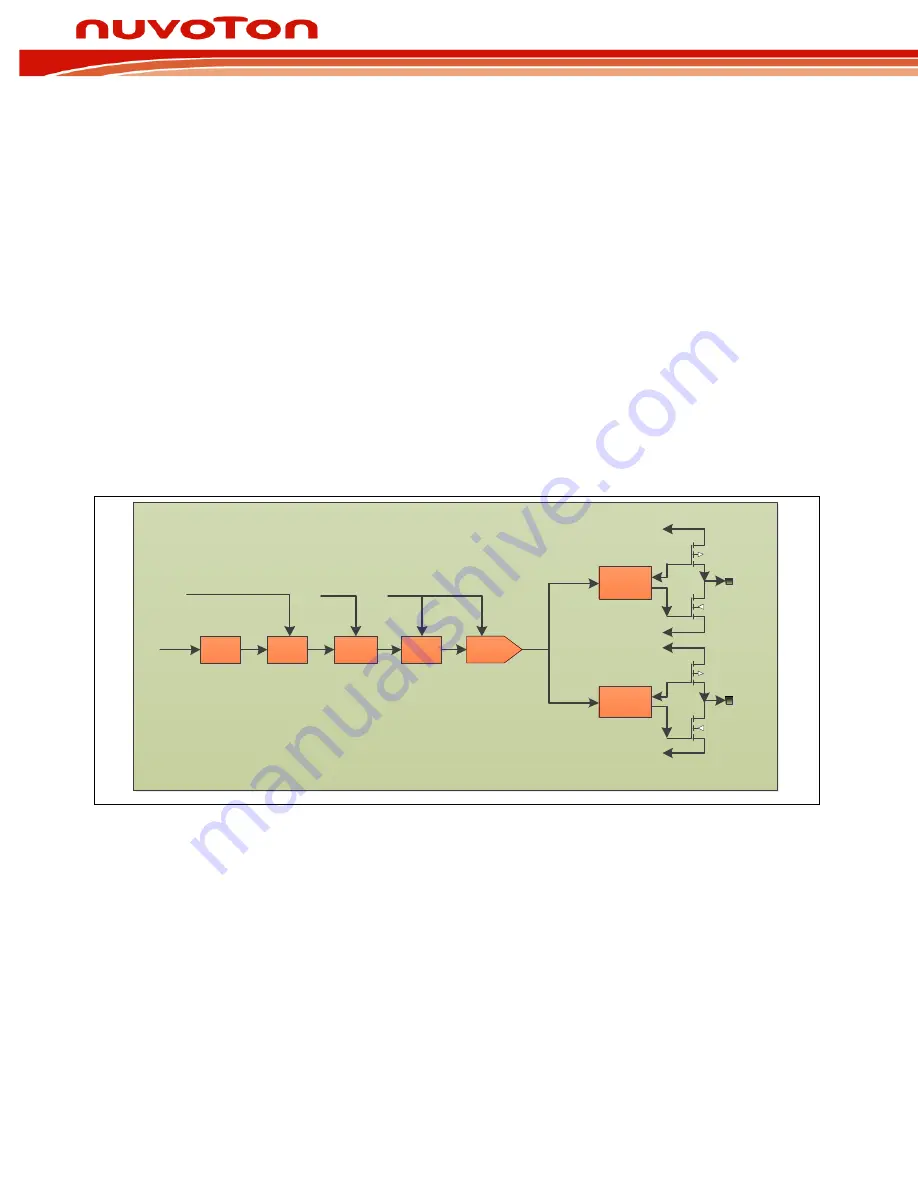

Block Diagram

Non-

overlap

Gen.

VSSSPK

VCCSPK

Non-

overlap

Gen.

VSSSPK

VCCSPK

SPK+

SPK-

SD

Modulator

CIC

Filter

BIQ

VOL

FIFO

APB Bus

PDMA

Interface

DPWM->CTL.DPWMEN

VOLCTRL->EN.DPWMVOLEN

BIQ->CTL.BIQEN

Figure 7-5 DPWM Block Diagram

7.3.4

Operation

The DPWM block receives audio data by writing PCM audio to the FIFO. FIFO is accessed through

PDMA for ease of streaming. The audio stream is sampled by a zero-order hold and fed to an up-

sampling Cascaded Integrator Comb (CIC) filter with an up-sampling ratio of 64. The signal is then

modulated and sent to the driver stage through a non-overlap circuit. Master clock rate of the Delta-

Sigma modulator is controlled by DPWM_CLK. This clock can be HCLK/(1) or HXT (refer to

CLK_CLKSEL1). Ultimate SNR (Signal-to-Noise Ratio) is determined by the time resolution of the

master clock.