ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 463 -

Revision 2.4

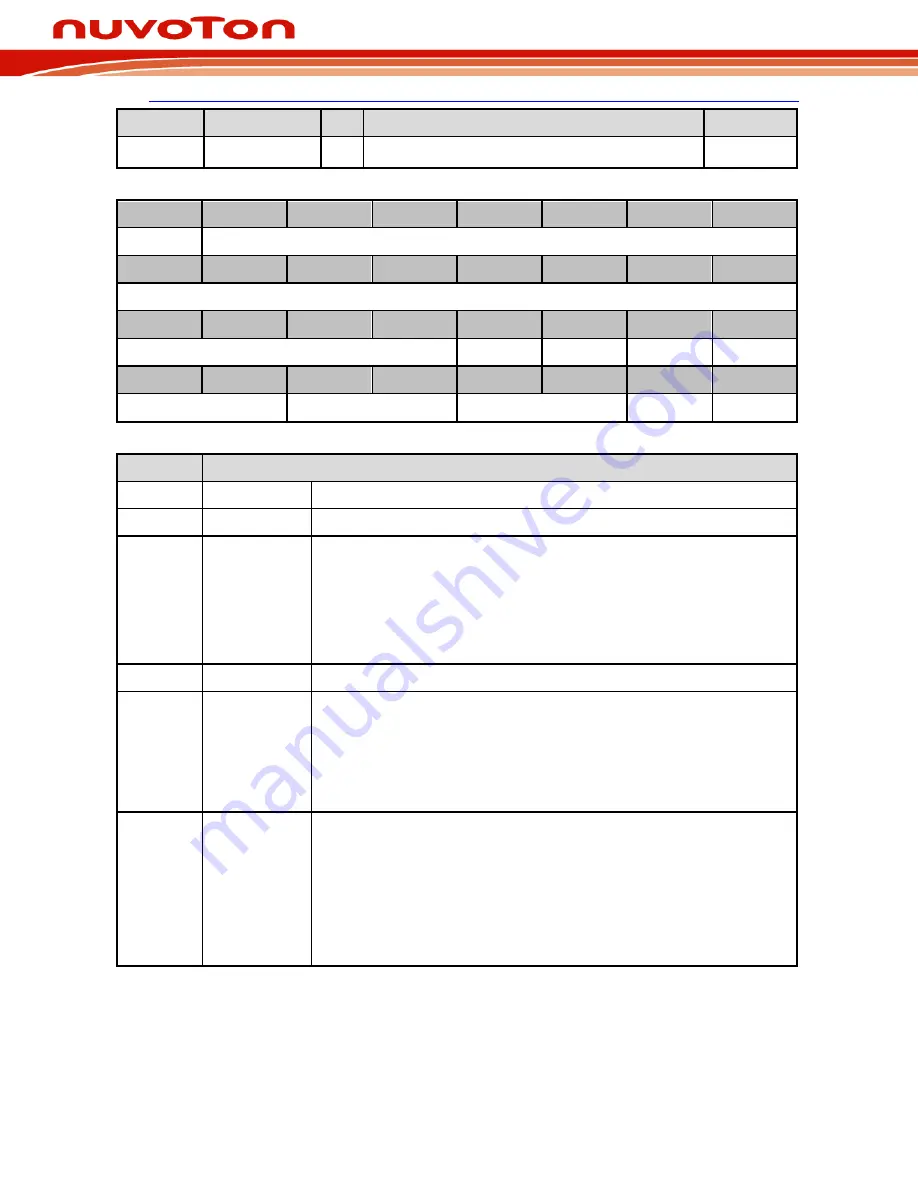

SAR ADC Control Register(SARADC_CTL)

Register

Offset

R/W

Description

Reset Value

SARADC_CTL

SA0x60 R/W

SAR ADC Control Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

SWTRG

Reserved

PDMAEN

HWTRGEN

7

6

5

4

3

2

1

0

HWTRGCOND

HWTRGSEL

OPMODE

ADCIE

ADCEN

Bits

Description

[31]

Reserved

Reserved

[30:12]

Reserved

Reserved

[11]

SWTRG

A/D Conversion Start

0 = Conversion stops and A/D converter enter idle state.

1 = Conversion starts.

SWTRG bit can be set to 1 from three sources: software, external pin STADC. SWTRG

will be cleared to 0 by hardware automatically at the ends of single mode and single-cycle

scan mode. In continuous scan mode, A/D conversion is continuously performed until

software writes 0 to this bit or chip reset.

[10]

Reserved

Reserved

[9]

PDMAEN

PDMA Transfer Enable Bit

0 = PDMA data transfer Disabled.

1 = PDMA data transfer in DAT 0~11 Enabled.

When A/D conversion is completed, the converted data is loaded into DAT 0~11, software

can enable this bit to generate a PDMA data transfer request.

When PDMA=1, software must set ADCIE=0 to disable interrupt.

[8]

HWTRGEN

Hardware Trigger Enable Bit

Enable or disable triggering of A/D conversion by hardware (external STADC pin or PWM

Center-aligned trigger).

0 = Disabled.

1 = Enabled.

SARADC hardware trigger function is only supported in single-cycle scan mode.

If hardware trigger mode, the SWTRG bit can be set to 1 by the selected hardware trigger

source.