ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 53 -

Revision 2.4

5.2.6

System Timer (SysTick)

The Cortex-M0 includes an integrated system timer, SysTick. SysTick provides a simple, 24-bit,

clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter

can be used in several different ways, for example:

An RTOS tick timer which fires at a programmable rate (for example 100Hz) and invokes a

SysTick routine.

A high speed alarm timer using Core clock.

A variable rate alarm or signal timer – the duration range dependent on the reference clock used

and the dynamic range of the counter.

A simple counter. Software can use this to measure time to completion and time used.

An internal clock source control based on missing/meeting durations. The COUNTFLAG bit-field

in the control and status register can be used to determine if an action completed within a set

duration, as part of a dynamic clock management control loop.

When enabled, the timer will count down from the value in the SysTick Current Value Register

(SYST_CVR) to zero, reload (wrap) to the value in the SysTick Reload Value Register (SYST_RVR)

on the next clock edge, then decrement on subsequent clocks. When the counter transitions to zero,

the COUNTFLAG status bit is set. The COUNTFLAG bit clears on reads.

The SYST_CVR value is UNKNOWN on reset. Software should write to the register to clear it to zero

before enabling the feature. This ensures the timer will count from the SYST_RVR value rather than

an arbitrary value when it is enabled.

If the SYST_RVR is zero, the timer will be maintained with a current value of zero after it is reloaded

with this value. This mechanism can be used to disable the feature independently from the timer

enable bit.

In DEEPSLEEP and power down modes, the SysTick timer is disabled so cannot be used to wake up

the device.

For more detailed information, please refer to the documents “

ARM®

Cortex™-M0 Technical

Reference Manual” and “

ARM® v6-M Architecture Reference Manual”.

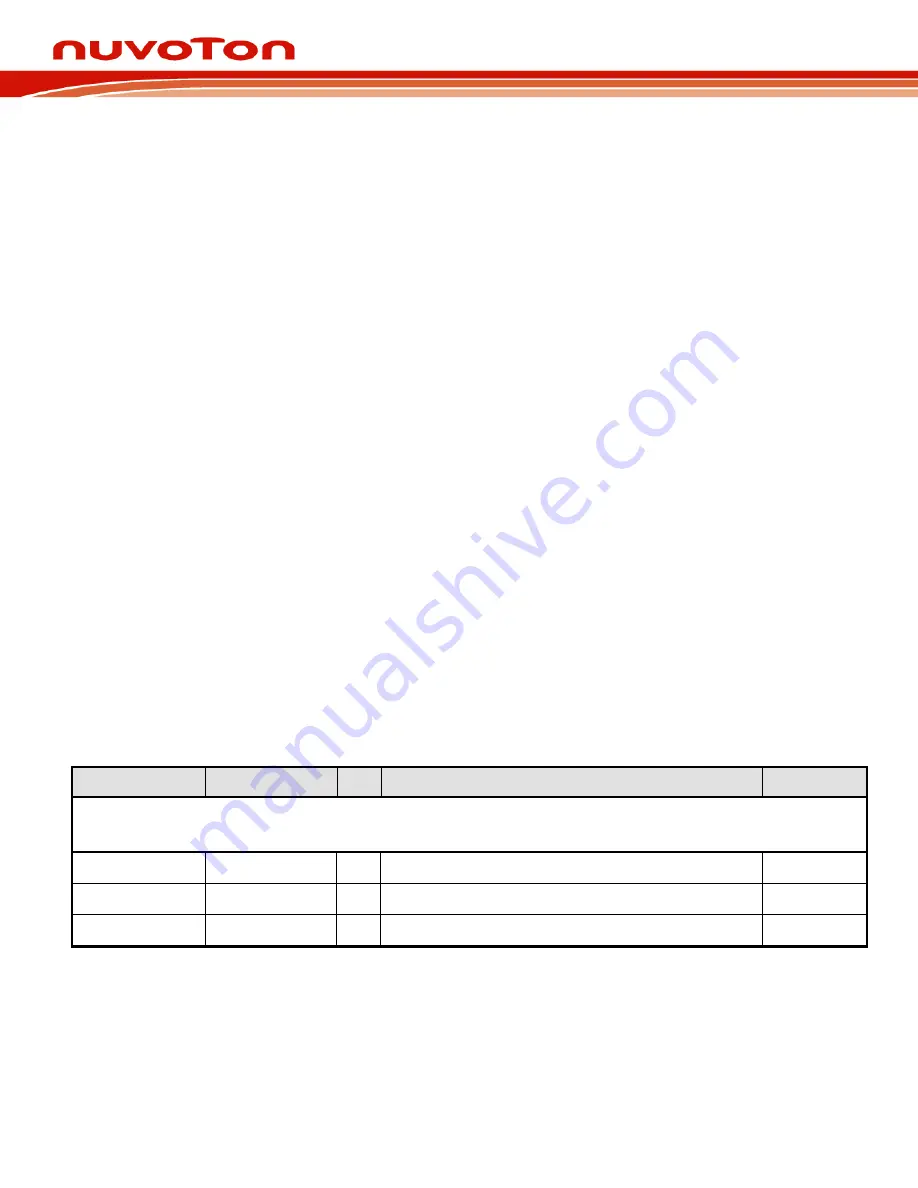

5.2.6.1

System Timer Control Register Map

R

: read only,

W

: write only,

R/W

: both read and write,

W&C

: Write 1 clear

Register

Offset

R/W

Description

Reset Value

SYSTICK Base Address:

SYSTICK_BA = 0xE000_E000

SYST_CSR

SYS0x10 R/W

SysTick Control and Status Register

0x0000_0000

SYST_RVR

SYS0x14 R/W

SysTick Reload value Register

0xXXXX_XXXX

SYST_CVR

SYS0x18 R/W

SysTick Current value Register

0xXXXX_XXXX

Note: In BSP register structure, the prefix is structure name, and register will be no prefix, for example

SYSTICK_ is the prefix, SYSTICK_CSR will be SYSTICK->CSR

5.2.6.2

System Timer Control Register Description