ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 294 -

Revision 2.4

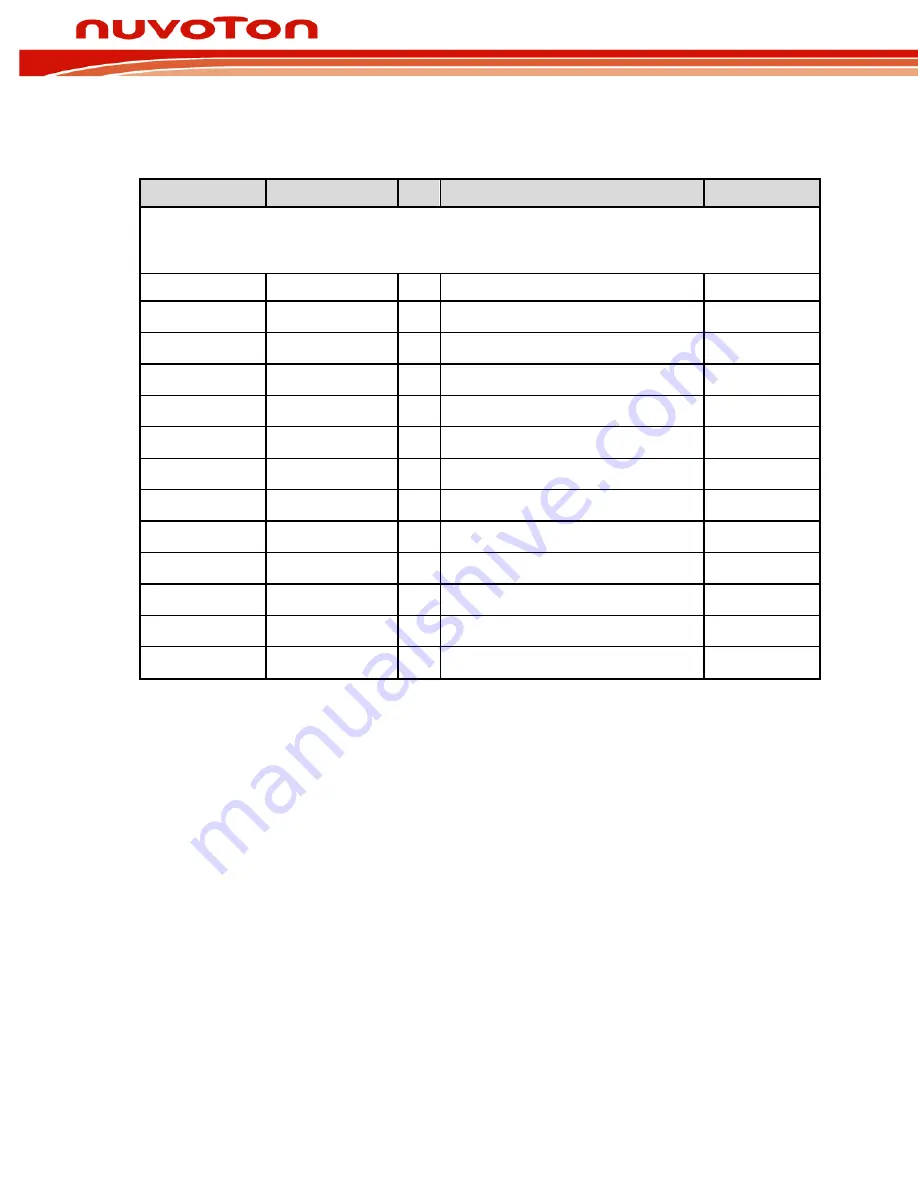

5.13.6 Register Map

R

: read only,

W

: write only,

R/W

: both read and write

Register

Offset

R/W

Description

Reset Value

UART Base Address:

UARTn_BA = 0x400 (n*0x8000)

n=0,1

UARTn_DAT

U0x00

R/W

UART Receive/Transfer FIFO Register.

0x0000_0000

UARTn_INTEN

U0x04

R/W

UART Interrupt Enable Register.

0x0000_0000

UARTn_FIFO

U0x08

R/W

UART FIFO Control Register.

0x0000_0000

UARTn_LINE

U0x0C

R/W

UART Line Control Register.

0x0000_0000

UARTn_MODEM

U0x10

R/W

UART Modem Control Register.

0x0000_0000

UARTn_MODEMSTS

U0x14

R/W

UART Modem Status Register.

0x0000_0010

UARTn_FIFOSTS

U0x18

R/W

UART FIFO Status Register.

0x1040_4000

UARTn_INTSTS

U0x1C

R/W

UART Interrupt Status Register.

0x0000_0002

UARTn_TOUT

U0x20

R/W

UART Time Out Register

0x0000_0000

UARTn_BAUD

U0x24

R/W

UART Baud Rate Divisor Register

0x0F00_0000

UARTn_IRDA

U0x28

R/W

UART IrDA Control Register.

0x0000_0040

UARTn_ALTCTL

U0x2C

R/W

UART LIN Control Register.

0x0000_0000

UARTn_FUNCSEL

U0x30

R/W

UART Function Select Register.

0x0000_0000