ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

232

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

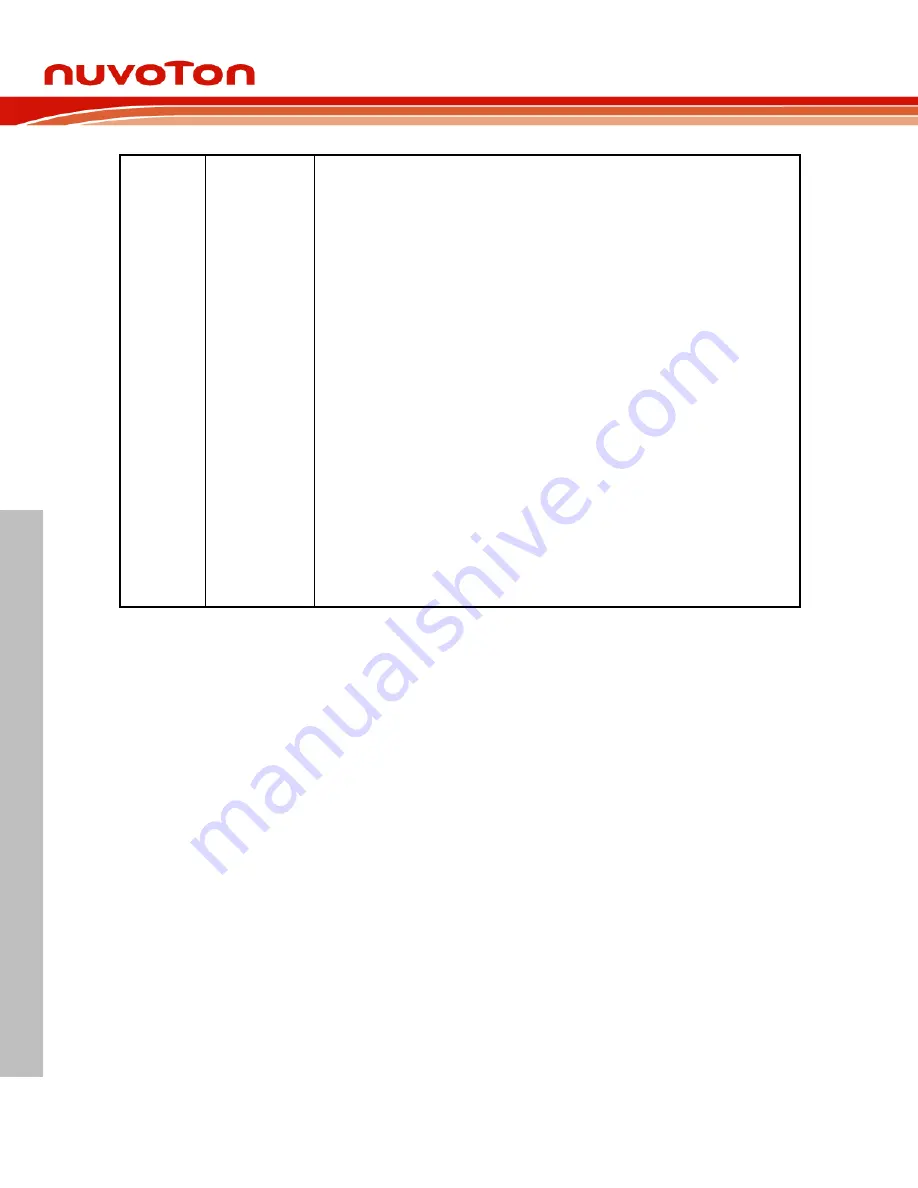

[3:0]

CYCLE

Flash Access Cycle Control (Write Protect)

This register is updated automaticly by hardware while FCYCDIS (FMC_ISPSTS[4]) is 0,

and updated by software while auto-tuning function disabled ( FADIS (FMC_CYCCTL[8]) is

1)

0000 = CPU access with zero wait cycle ; flash access cycle is 1;.

The HCLK working frequency range is <27 MHz; Cache is disabled by hardware.

0001 = CPU access with one wait cycle if cache miss; flash access cylcle is 1;.

The HCLK working frequency range range is<27 MHz

0010 = CPU access wtih two wait cycles if cahce miss; flash access cycle is 2;.

The optimized HCLK working frequency range is 27~54 MHz

0011 = CPU access with three wait cycles if cache miss; flash access cylcle is 3;.

The optimized HCLK working frequency range is 54~81 MHz

0100 = CPU access with four wait cycles if cahce miss; flash access cycle is 4;.

The optimized HCLK working frequency range is81~108 MHz

0101 = CPU access with five wait cycles if cache miss; flash access cylcle is 5;.

The optimized HCLK working frequency range is 108~135 MHz

0110 = CPU access with six wait cycles if cahce miss; flash access cycle is 6;.

The optimized HCLK working frequency range is 135~162 MHz

0111 = CPU access with seven wait cycles if cahce miss; flash access cycle is 7;.

The optimized HCLK working frequency range is 162~192 MHz

1000 = CPU access with eight wait cycles if cache miss; flash access cylcle is 8;.

The optimized HCLK working frequency range is >192 MHz

Note:

This bit is write protected. Refer to the SYS_REGLCTL register.