ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

271

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

Time-out counter

TOC0

(PDMA_TOC0_1[15:0])

TOUTEN0

(PDMA_TOUTEN[0])

1 2 3 4 5 0 1 2 3

0

5

0 1 2 3 0

x

Peripheral request

REQTOF0

(PDMA_INTSTS[8])

Time-out clock

(HCLK/2^8)

TOUTPSC0

(PDMA_TOUTPSC[2:0])

0

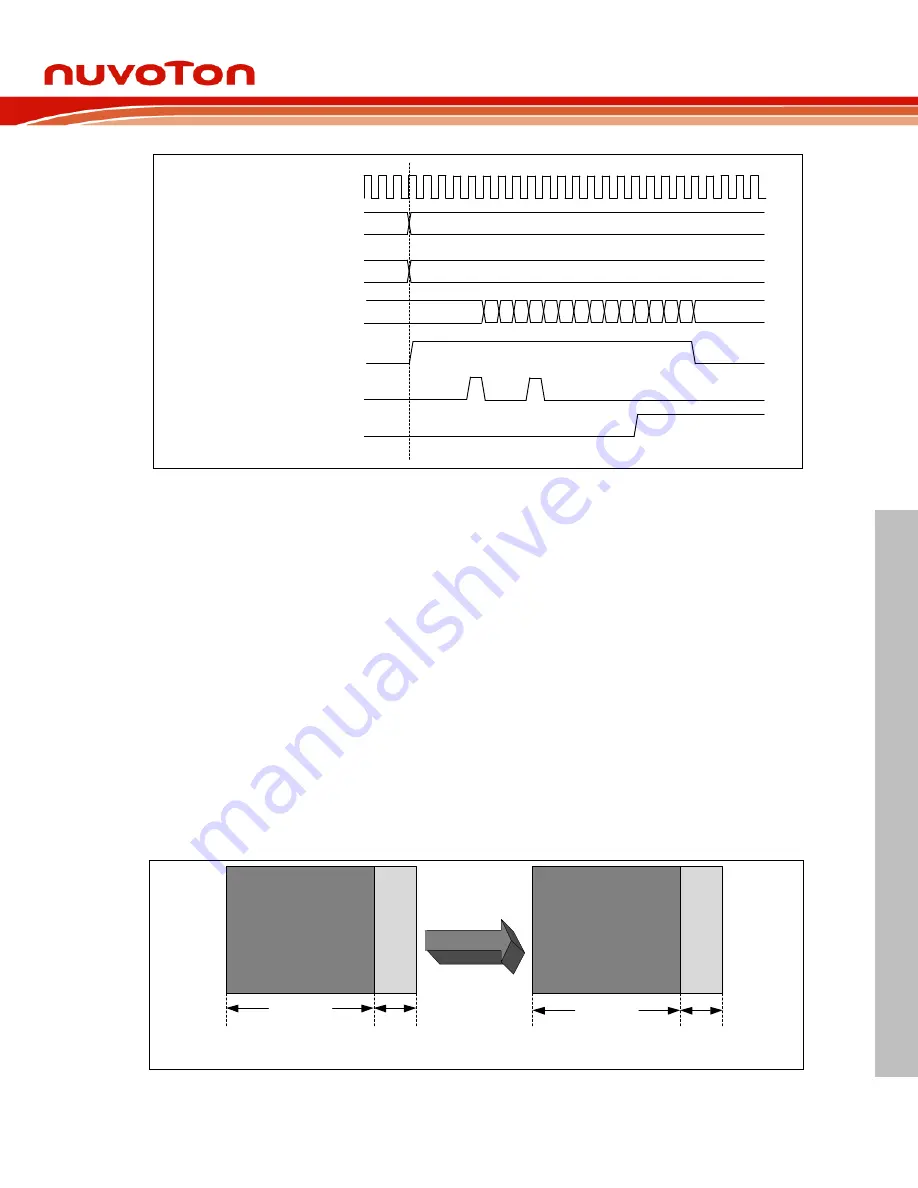

Figure 6.6-7 Example of PDMA Channel 0 Time-out Counter Operation

6.6.5.5

Stride Function

The PDMA support channel 0 to channel 5 six channels with stride function. The stride function can

transfers data from one address to another address and can support block transfer with stride.

When operating in stride function, the transfer address can be fixed or incremented successively.

Setting STRIDE_EN (PDMA_DSCTn_CTL[15]) to enable stride function, and then write a valid

source address to the PDMA_DSCTn_SA register and a source address offset count to SASOL

(PDMA_ASOCRn[15:0]) register, a destination address to the PDMA_DSCTn_DA register and a

destination address offset count to DASOL (PDMA_ASOCRn[31:16]), and a transfer count to the

TXCNT (PDMA_DSCTn_CTL) register and a stride transfer count to STC (PDMA_STCn[15:0]).

Next, trigger the SWREQn (PDMA_SWREQ[5:0]). The DMA will continue the transfer until TXCNT

(PDMA_DSCTn_CTL) count down to zero. The Figure 6.6-8 shows the block transfer relationship

between source memory and destination memory. Stride function also supports peripheral to

memory or memory to peripheral transfer.

Please note that stride mode must be operated in burst mode (TXTYPE (PDMA_DSCTx_CTL[2])

= 0), and the transfer count (TXCNT (PDMA_DSCTx_CTL[31:16])) should be less than burst size

(BURSIZE (PDMA_DSCTx_CTL[6:4])), and STC (PDMA_STCRx[15:0]) must be greater than or

equal to 1.

Source Memory

Destination Memory

STC

STC

SASOL

DASOL

Figure 6.6-8 Stride Function Block Transfer