ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

360

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

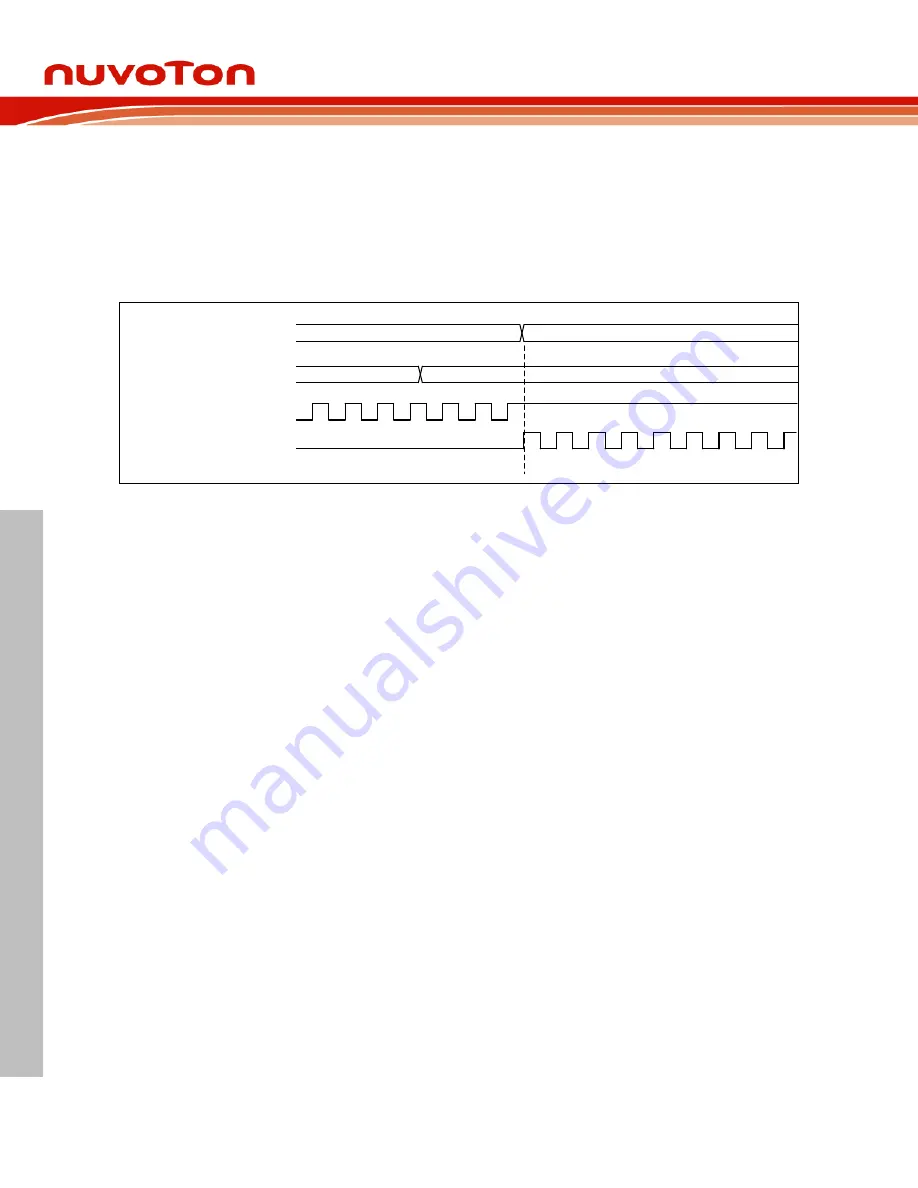

6.7.6.16 PWM Mask Output Control

PWMx_CH0/CH1 output value can be masked to specified logic states by setting MSKEN0/1

(TIMERx_PWMMSKEN[1:0]) and MSKDAT0/1 (TIMERx_PWMMSK[1:0]). The PWM output mask

function is useful when controlling various types of Electrically Commutated Motor (ECM) like a

BLDC motor. Figure 6.7-29 shows an example of PWM output mask control in PWMx_CH0 and

PWMx_CH1.

PWMx_CH0

MSKDAT1/0

(TIMERx_PWMMSK[1:0])

0x0

0x1

MSKEN1/0

(TIMERx_PWMMSKEN[1:0])

PWMx_CH1

0x2 (mask channel 1)

0x1 (mask channel 0)

Figure 6.7-29 PWM Output Mask Control Waveform

6.7.6.17 Polarity Control

Each PWMx_CH0 and PWMx_CH1 has an independent polarity control to configure the polarity of

the active state of PWM output. User can control polarity state of PWMx_CH0 on PINV0

(TIMERx_PWMPOLCTL[0]) and PWMx_CH1 on PINV1 (TIMERx_PWMPOLCTL[1]). Figure 6.7-30

shows the PWMx_CH0 and PWMx_CH1 output with polarity control and dead-time insertion.