ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

367

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

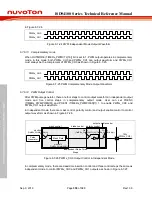

Register

Offset

R/W Description

Reset Value

TIMER Base Address:

TMR01_BA = 0x4005_0000

TMR23_BA = 0x4005_1000

TIMER3_PWMPOLCTL

T0x174

R/W Timer3 PWM Pin Output Polar Control Register

0x0000_0000

TIMER3_PWMPOEN

T0x178

R/W Timer3 PWM Pin Output Enable Register

0x0000_0000

TIMER3_PWMINTEN0

T0x180

R/W Timer3 PWM Interrupt Enable Register 0

0x0000_0000

TIMER3_PWMINTSTS0

T0x188

R/W Timer3 PWM Interrupt Status Register 0

0x0000_0000

TIMER3_PWMADCTS

T0x190

R/W Timer3 PWM ADC Trigger Source Select Register

0x0000_0000

TIMER3_PWMSCTL

T0x194

R/W Timer3 PWM Synchronous Control Register

0x0000_0000

TIMER3_PWMSSTRG

T0x198

W

Timer3 PWM Synchronous Start Trigger Register

0x0000_0000

TIMER3_PWMSTATUS

T0x19C R/W Timer3 PWM Status Register

0x0000_0000

TIMER3_PWMPBUF

T0x1A0 R

Timer3 PWM Period Buffer Register

0x0000_0000

TIMER3_PWMCMPBUF

T0x1A4 R

Timer3 PWM Comparator Buffer Register

0x0000_0000

Note:

1.

Any register not listed here is reserved and must not be written. The result of a read operation on these bits is undefined.

2.

The reserved register fields that listed in register description must be written to their reset value. Writing reserved fields with

other than reset values may produce undefined results.