ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

390

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

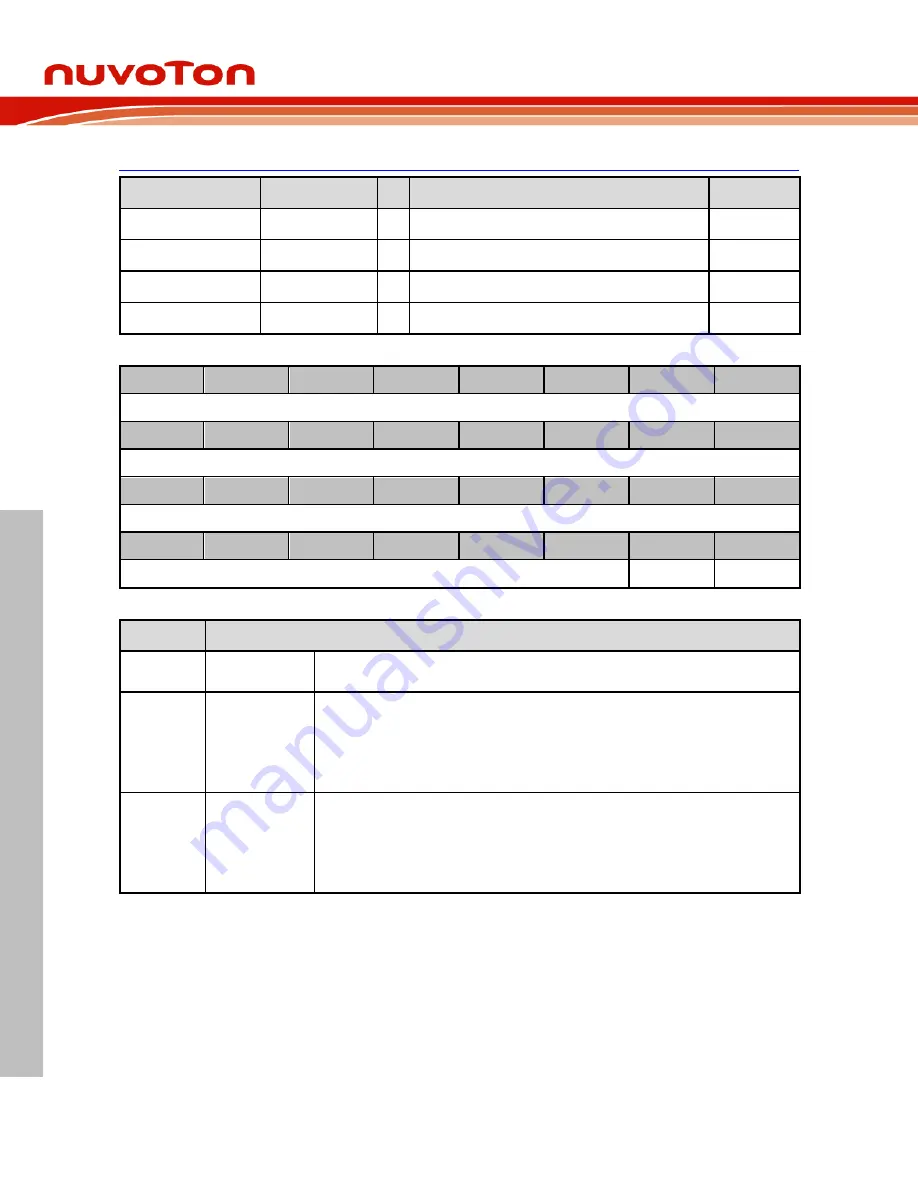

Timer PWM Output Mask Enable Register (TIMERx PWMMSKEN)

Register

Offset

R/W Description

Reset Value

TIMER0_PWMMSKEN

T0x60

R/W Timer0 PWM Output Mask Enable Register

0x0000_0000

TIMER1_PWMMSKEN

T0x160

R/W Timer1 PWM Output Mask Enable Register

0x0000_0000

TIMER2_PWMMSKEN

T0x60

R/W Timer2 PWM Output Mask Enable Register

0x0000_0000

TIMER3_PWMMSKEN

T0x160

R/W Timer3 PWM Output Mask Enable Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Reserved

MSKEN1

MSKEN0

Bits

Description

[31:2]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[1]

MSKEN1

PWMx_CH1 Output Mask Enable Bit

The PWMx_CH1 output signal will be masked when this bit is enabled. The PWMx_CH1 will

output MSKDAT1 (TIMER_PWMMSK[1]) data.

0 = PWMx_CH1 output signal is non-masked.

1 = PWMx_CH1 output signal is masked and output MSKDAT1 data.

[0]

MSKEN0

PWMx_CH0 Output Mask Enable Bit

The PWMx_CH0 output signal will be masked when this bit is enabled. The PWMx_CH0 will

output MSKDAT0 (TIMER_PWMMSK[0]) data.

0 = PWMx_CH0 output signal is non-masked.

1 = PWMx_CH0 output signal is masked and output MSKDAT0 data.