ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

410

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

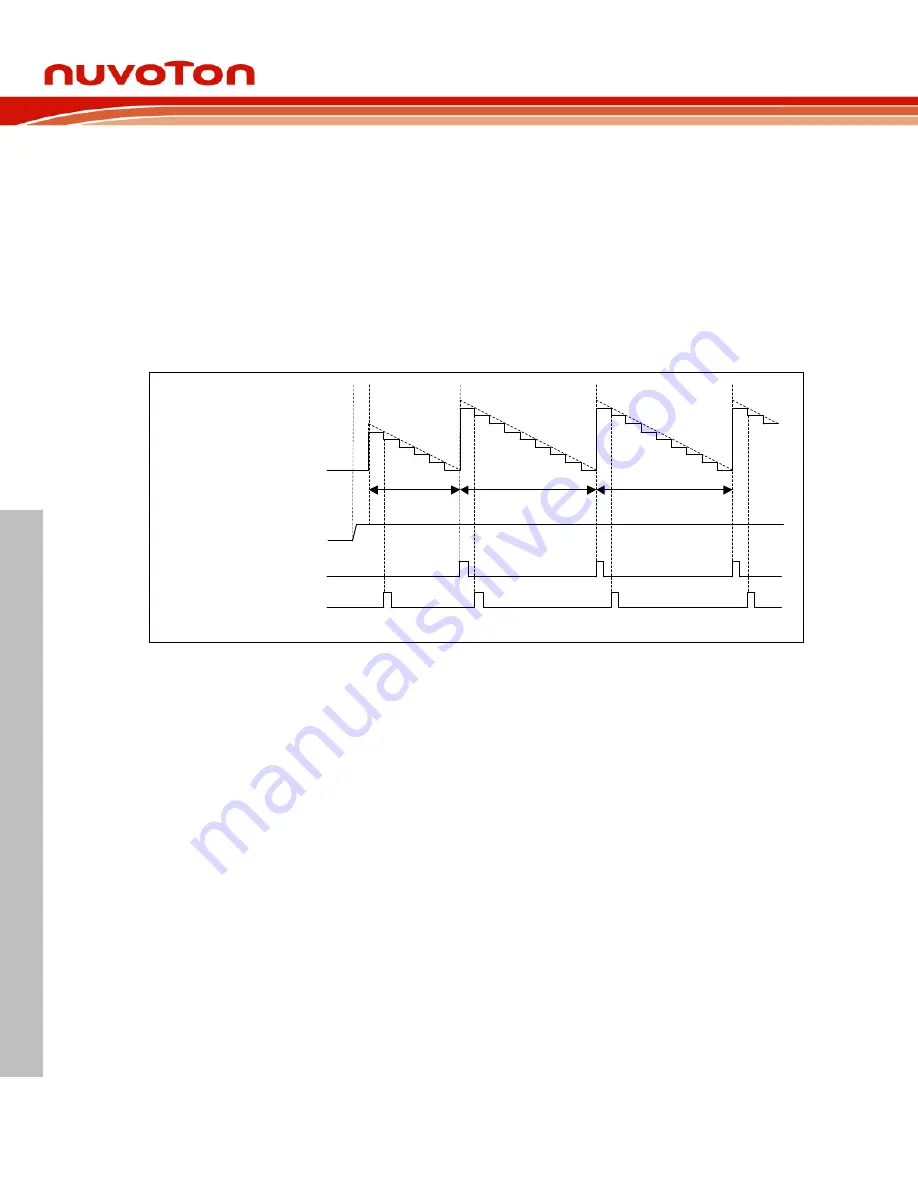

6.8.5.4

Down Counter Type

When PWM counter is set to down counter type, CNTTYPEn (PWM_CTL1[2n+1:2n], n = 0,1..5) is

0x1, it starts down-counting from PERIOD to zero to complete a PWM period. The current counter

value can be read from CNT (PWM_CNTn[15:0]) bits. PWM generates zero point event when the

counter counts to 0 and prescale counts to 0. PWM generates period point event when the counter

counts to PERIOD and prescale counts to 0. The Figure 6.8-9 shows an example of down counter,

wherein

PWM period time = (1) * (1) * PWM0_CLK.

0

1

2

3

4

X

0

1

2

3

4

5

6

7

8

0

1

2

3

4

5

6

7

8

6

7

8

PWM Period

PWM Period

PWM Period

PERIOD = 5

PERIOD = 8

PERIOD = 8

zero point event

period point event

CNT

(PWM_CNTn[15:0])

CNTENn

(PWM_CNTEN[n])

5

Note:

n denotes channel 0,1..5

Figure 6.8-9 PWM Down Counter Type

6.8.5.5

Up-Down Counter Type

When PWM counter is set to up-down count type, CNTTYPEn (PWM_CTL1[2n+1:2n], n = 0,1..5)

is 0x2, it starts counting-up from zero to PERIOD and then starts counting down to zero to complete

a PWM period. The current counter value can be read from CNT (PWM_CNTn[15:0]) bits. PWM

generates zero point event when the counter counts to 0 and prescale counts to 0. PWM generates

center point event when the counter counts to PERIOD. The Figure 6.8-10 shows an example of

up-down counter, wherein

PWM period time =(PERIOD) * (1) * PWM0_CLK.

The DIRF (PWM_CNTn[16]) bit is counter direction indicator flag, where high is up counting, and

low is down counting.