ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

436

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

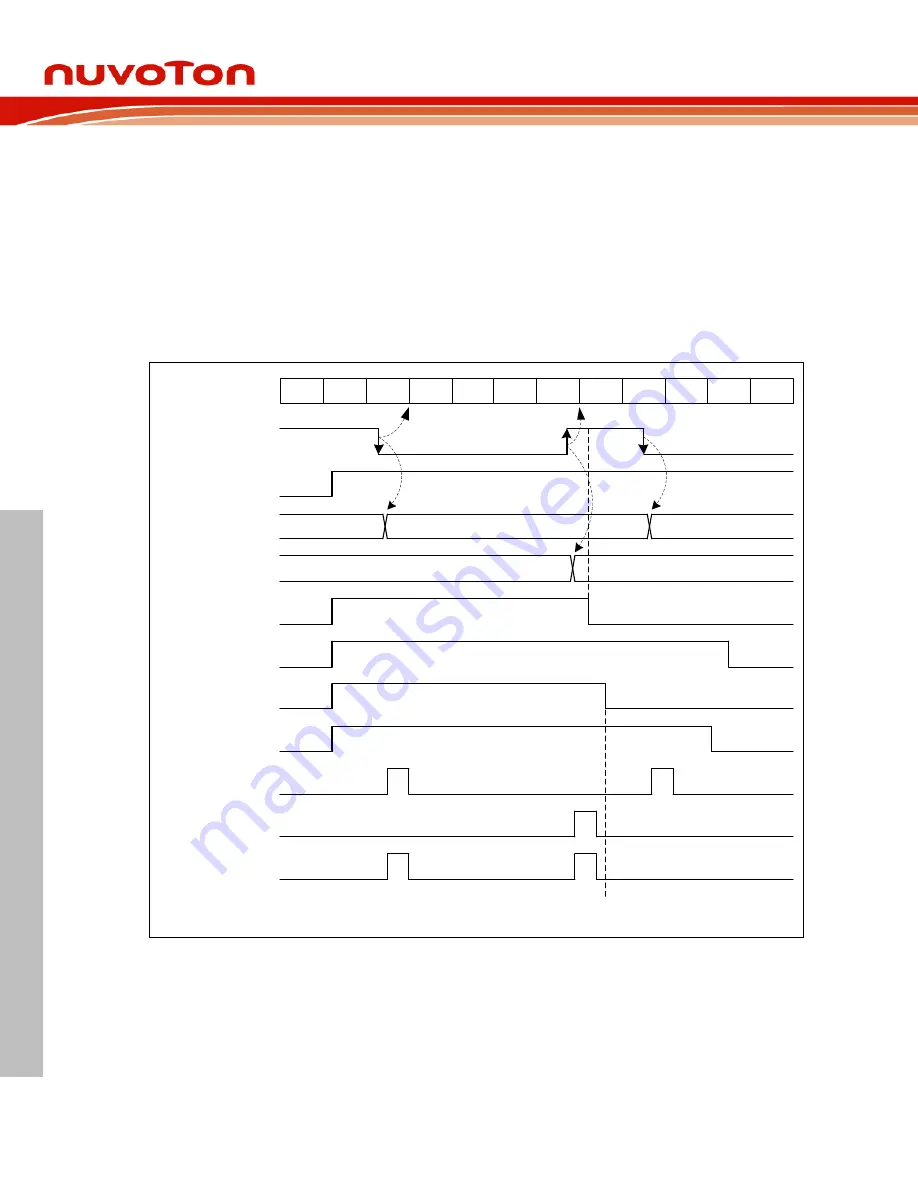

the rising edge at channel n is detected, the corresponding CRLIFn (PWM_CAPIF[5:0]) bit is set by

hardware. Similarly, a falling edge detection at channel n causes the corresponding CFLIFn

(PWM_CAPIF[13:8]) bit is set by hardware. CRLIFn and CFLIFn bits can be cleared by software

by writing ‘1’. If the CRLIFn bit is set and the CAPRIENn bit is enabled, the capture function

generates an interrupt. If the CFLIFn bit is set and the CAPFIENn bit is enabled, the interrupt also

happens.

A condition which is not shown in this figure is: if the rising latch happens again when the CRLIFn

bit is already set, the Overrun status CRLIFOVn (PWM_CAPSTS[5:0]) bit will be set to 1 by

hardware to indicate the CRLIF flag overrunning. Also, if the falling latch happens again, the same

hardware operation occurs for the CFLIF interrupt flag and the Overrun status CFLIFOVn

(PWM_CAPSTS[13:8]).

Note:

n denotes 0 to 5

8

7

6

5

4

3

2

1

8

7

6

5

PWM counter

1

7

Capture Input

PWM_FCAPDATn

5

PWM_RCAPDATn

Capture interrupt

CAPFIENn

CAPRIENn

CAPINENn

Clear by S/W

CFLIFn

CRLIFn

Reload (PERIOD = 8)

Reload

Clear by S/W

Falling Latch

Falling Latch

Rising Latch

FCRLDENn

RCRLDENn

Figure 6.8-41 Capture Operation Waveform

The capture pulse width can be calculated according to the following formula:

For the negative pulse case, the channel low pulse width is calculated as (PWM_P 1 -

PWM_RCAPDATn) PWM counter time, where one PWM counter time is (1) *

PWM0_CLK clock time. In Figure 6.8-41, the low pulse width is 8+1-5 = 4 PWM counter time.

For the positive pulse case, the channel high pulse width is calculated as (PWM_P 1 -