ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

51

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

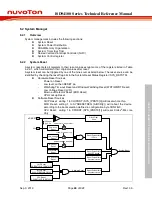

WDT_CTL

except bit 1 and bit 7

0x0700

0x0700

0x0700

0x0700

0x0700

-

0x0700

-

-

WDT_ALTCTL

0x0000

0x0000

0x0000

0x0000

0x0000

-

0x0000

-

-

WWDT_RLDCNT

0x0000

0x0000

0x0000

0x0000

0x0000

-

0x0000

-

-

WWDT_CTL

0x3F0800 0x3F0800 0x3F0800 0x3F0800 0x3F0800 -

0x3F0800

-

-

WWDT_STATUS

0x0000

0x0000

0x0000

0x0000

0x0000

-

0x0000

-

-

WWDT_CNT

0x3F

0x3F

0x3F

0x3F

0x3F

-

0x3F

-

-

BS

(FMC_ISPCTL[1])

Reload

from

CONFIG0

Reload

from

CONFIG0

Reload

from

CONFIG0

Reload

from

CONFIG0

Reload

from

CONFIG0

-

Reload

from

CONFIG0

-

-

FMC_DFBA

Reload

from

CONFIG1

Reload

from

CONFIG1

Reload

from

CONFIG1

Reload

from

CONFIG1

Reload

from

CONFIG1

-

Reload

from

CONFIG1

-

-

CBS

(FMC_ISPSTS[2:1))

Reload

from

CONFIG0

Reload

from

CONFIG0

Reload

from

CONFIG0

Reload

from

CONFIG0

Reload

from

CONFIG0

-

Reload

from

CONFIG0

-

-

VECMAP

(FMC_ISPSTS[23:9])

Reload

based on

CONFIG0

Reload

based on

CONFIG0

Reload

based on

CONFIG0

Reload

based on

CONFIG0

Reload

based on

CONFIG0

-

Reload

based on

CONFIG0

-

-

Other Peripheral

Registers

Reset Value

-

FMC Registers

Reset Value

Note:

‘-‘ means that the value of register keeps original setting.

Table 6.2.2-1 Reset Value of Registers

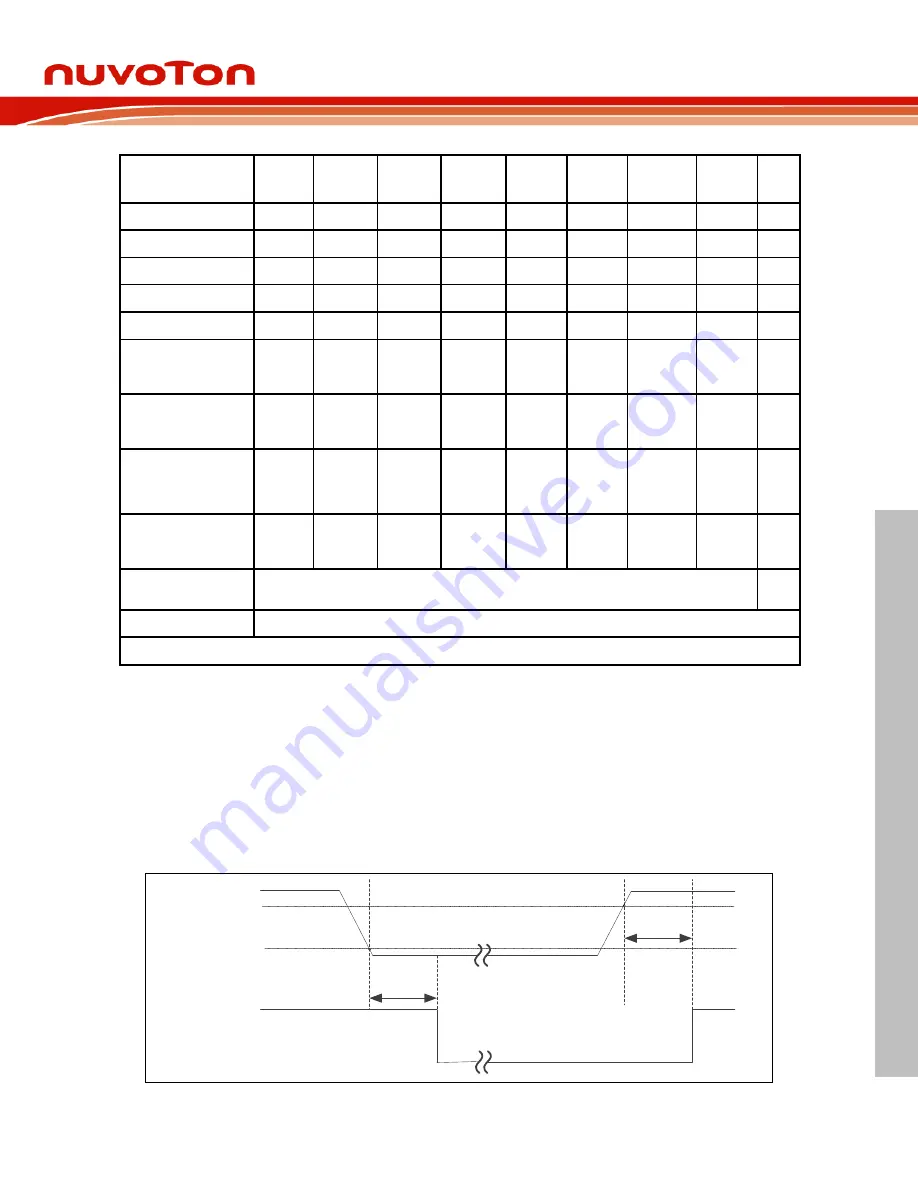

6.2.2.1 nRESET Reset

nRESET is triggered by pulling nRESET pin low. nRESET pin is an asynchronous reset input pin

so that it can be used to reset the system any time.

Pull nRESET pin to < 0.3* V

DD

for > 66us will reset the chip. Once entered reset state, only high

voltage (> 0.7* V

DD

) presented on nRESET pin for >66us can exit the reset state. See nRESET

reset waveform in Figure 6.2-2.

After an nRESET reset, the PINRF bit (SYS_RSTSTS[1]) will be set, indicating the previous reset

source is an nRESET reset. Writing 1 to PINRF clears the bit.

nRESET

0.3 V

DD

0.7 V

DD

nRESET Reset

66 us

66 us

Figure 6.2-2 nRESET Reset Waveform