ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

514

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

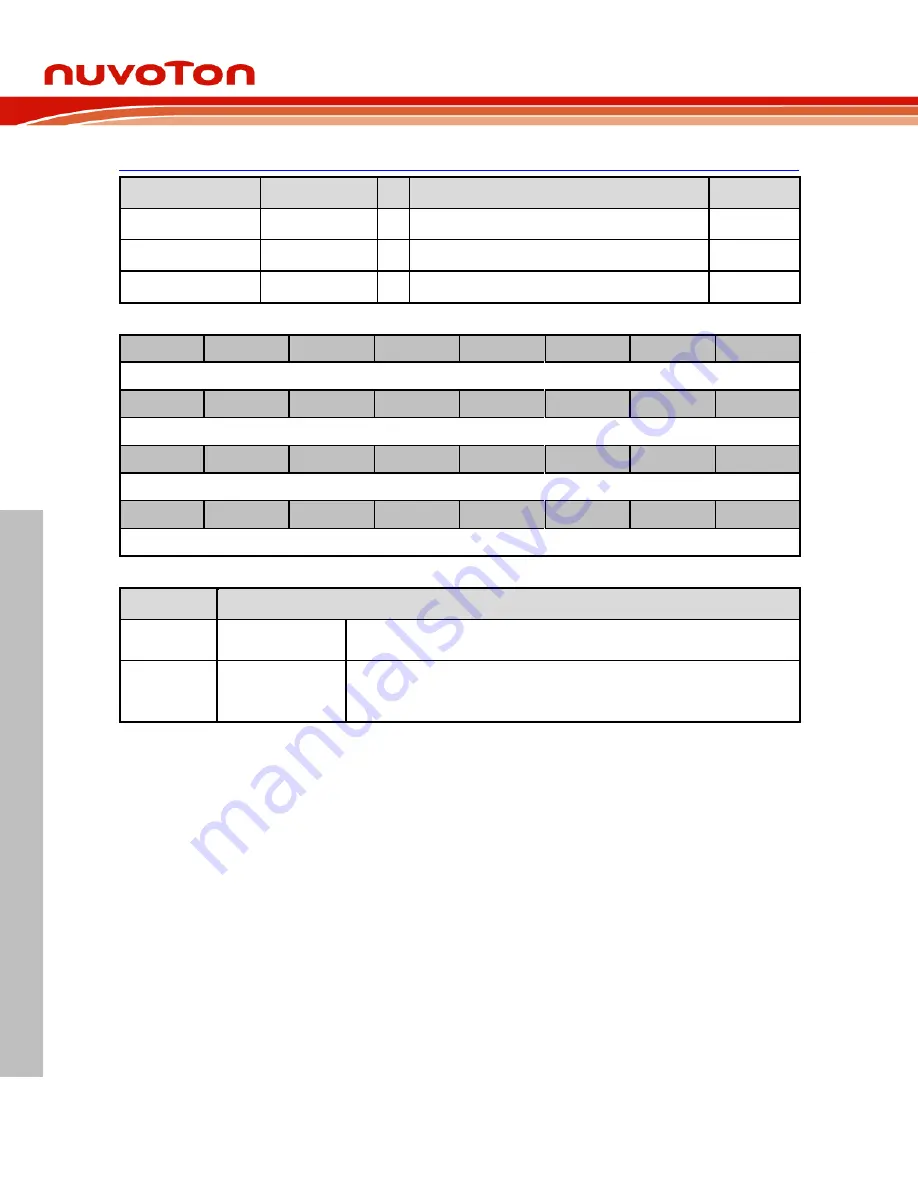

PWM Capture Channel 0_1, 2_3, 4_5 PDMA Register (PWM_PDMACAP 0_1, 2_3, 4_5)

Register

Offset

R/W Description

Reset Value

PWM_PDMACAP0_1

0x240

R

PWM Capture Channel 01 PDMA Register

0x0000_0000

PWM_PDMACAP2_3

0x244

R

PWM Capture Channel 23 PDMA Register

0x0000_0000

PWM_PDMACAP4_5

0x248

R

PWM Capture Channel 45 PDMA Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

CAPBUF

7

6

5

4

3

2

1

0

CAPBUF

Bits

Description

[31:16]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write

with reset value.

[15:0]

CAPBUF

PWM Capture PDMA Register (Read Only)

This register is use as a buffer to transfer PWM capture rising or falling data to memory

by PDMA.