ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

526

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

–

Enable WDT peripheral clock in WDTCKEN (CLK_APBCLK0[0]).

–

Force enable WDT controller after chip power-on or reset in CWDTEN[2:0]

(CWDTEN[2] is CONFIG0[31], CWDTEN[1:0] is CONFIG0[4:3])

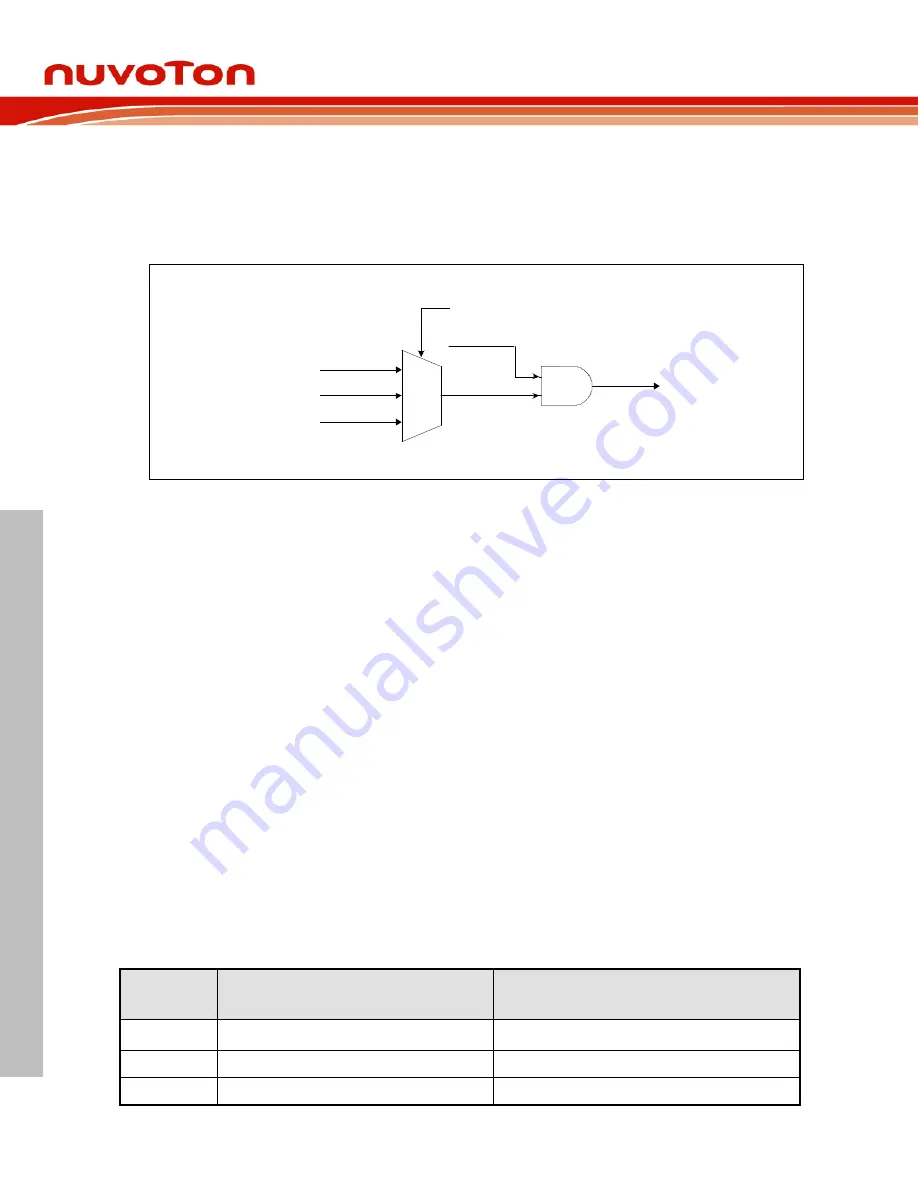

The WDT clock control are shown in Figure 6.9-2

10

01

HCLK/2048

WDTSEL (CLK_CLKSEL1[1:0])

WDT_CLK

11

10 kHz (LIRC)

32.768 kHz (LXT)

WDTCKEN (CLK_APBCLK0[0])

Figure 6.9-2 Watchdog Timer Clock Control

6.9.5

Functional Description

The WDT includes an 18-bit free running up counter with programmable time-out intervals. Table

6.9.5-1 shows the WDT time-out interval period selection and Figure 6.9-3 shows the WDT time-

out interval and reset period timing.

6.9.5.1

WDT Time-out Interrupt

Setting WDTEN (WDTCR[7]) to 1 will enable the WDT function and the WDT counter to start

counting up. There are eight time-out interval period can be selected by setting TOUTSEL

(WDTCR[10:8]). When the WDT up counter reaches the TOUTSEL (WDTCR[10:8]) settings, WDT

time-out interrupt will occur then WDT time-out interrupt flag IF (WDT_CTL[3]) will be set to 1

immediately. If INTEN (WDT_CTL[6]) is enabled, WDT time-out interrupt will inform to CPU.

6.9.5.2

WDT Reset Delay Period and Reset System

There is a specified T

RSTD

reset delay period follows the IF (WDT_CTL[3]) is setting to 1. User

should set RSTCNT (WDT_CTL[0]) to reset the 18-bit WDT up counter value to avoid generate

WDT time-out reset signal before the T

RSTD

reset delay period expires. Moreover, user should set

RSTDSEL (WDT_ALTCTL [1:0]) to select reset delay period to clear WDT counter. If the WDT up

counter value has not been cleared after the specific T

RSTD

delay period expires, the WDT control

will set RSTF (WDT_CTL[2]) to 1 if RSTEN (WDT_CTL[1]) bit is enabled, then chip enters to reset

state immediately. Refer to , T

RST

reset period will keep last 63 WDT clocks then chip restart

executing program from reset vector (0x0000_0000). The RSTF (WDT_CTL[2]) will keep 1 after

WDT time-out reset the chip, user can check RSTF (WDT_CTL[2]) by software to recognize the

system has been reset by WDT time-out reset or not.

TOUTSEL

Time-Out Interval Period

T

TIS

Reset Delay Period

T

RSTD

000

2

4

* T

WDT

(3/18/130/1026) * T

WDT

001

2

6

* T

WDT

(3/18/130/1026) * T

WDT

010

2

8

* T

WDT

(3/18/130/1026) * T

WDT