ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

578

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

HCLK

Start

D0~

D7

ADD

Address Match

Power-down mode

RS485WKF

UART0_RXD pin

STO

stable count

Note:

Stable count means HCLK source recovery stable count.

Figure 6.12-9 UART RS-485 AAD Mode Address Match Wake-up

RX FIFO threshold time-out wake-up:

RX FIFO Threshold Time-out Wake-up function can wake up the system if the device has not

received certain amount of data within specified time.

To enable RX FIFO Time-out Wake-up function:

-

Enable WKRFRTEN (UART_WKCTL[2]): RX FIFO Reached Threshold Wake-up Enable bit.

-

Enable WKTOUTEN (UART_WKCTL[4]): RX FIFO Time-out Wake-up Enable bit

-

Enable TOCNTEN (UART_INTEN[11]): RX FIFO Time-out Counter Enable bit

-

Configure RFITL (UART_FIFO[7:4]): RX FIFO Interrupt Trigger level

-

Configure TOIC (UART_TOUT[7:0]): Time-out Interrupt Comparator

Under this configuration, the time-out counter resets and starts counting incrementally whenever

RX FIFO receives new data. The counting clock frequency equals to the baud rate. When time-out

counter value equals to time-out value defined in TOIC, and the RX FIFO level does not reach the

threshold value defined in RFITL, it wakes up the system from power down mode, and flag

TOUTWKF(UART _WKSTS[4]) will be set.

Note:

The UART controller clock source should be selected as LXT in Power-down mode to receive

data.

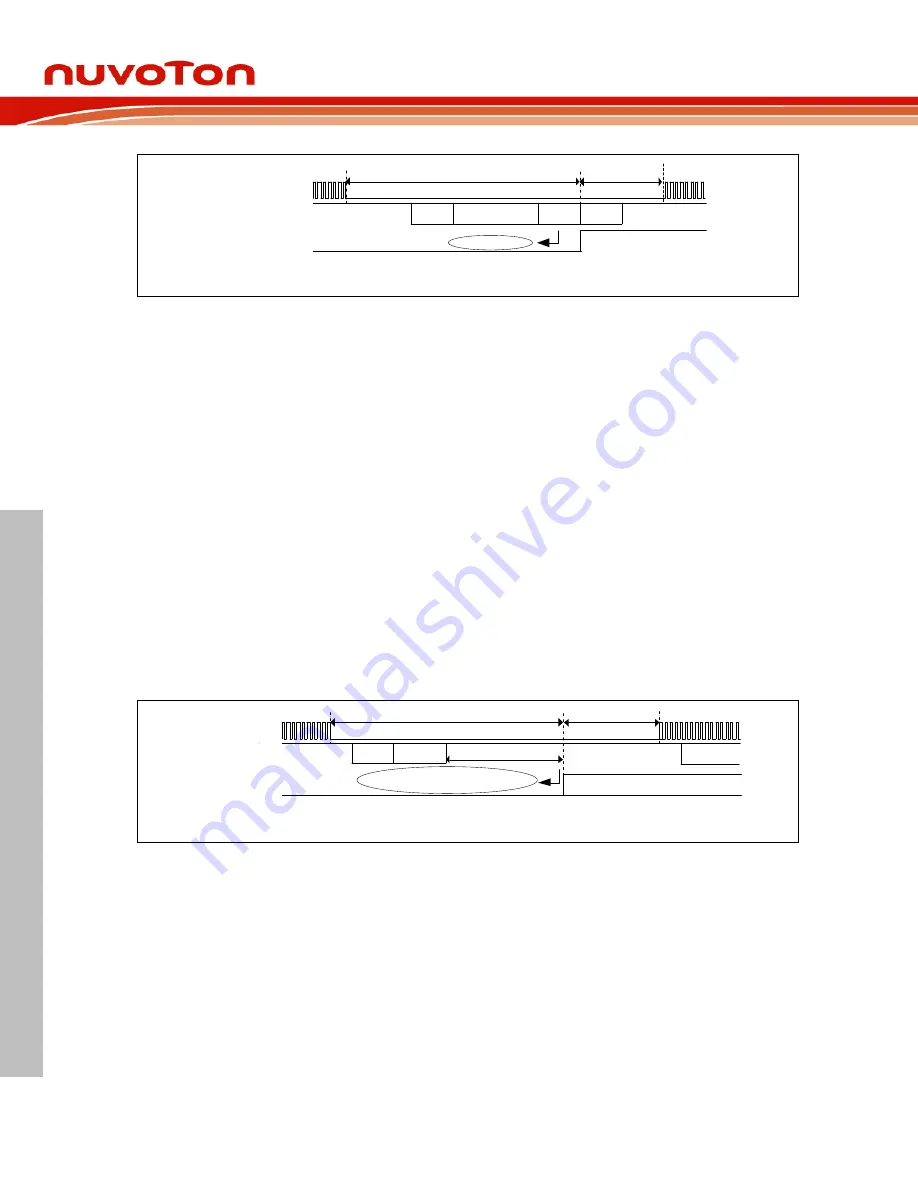

Power-down mode

HCLK

TOUTWKF

Start

DATA0

RX FIFO number not reached

RFITL and Time-out

UART0_RXD pin

Time-out

stable count

DATAx

Note:

Stable count means HCLK source recovery stable count.

Figure 6.12-10 UART RX FIFO threshold time-out wake-up