ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

583

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

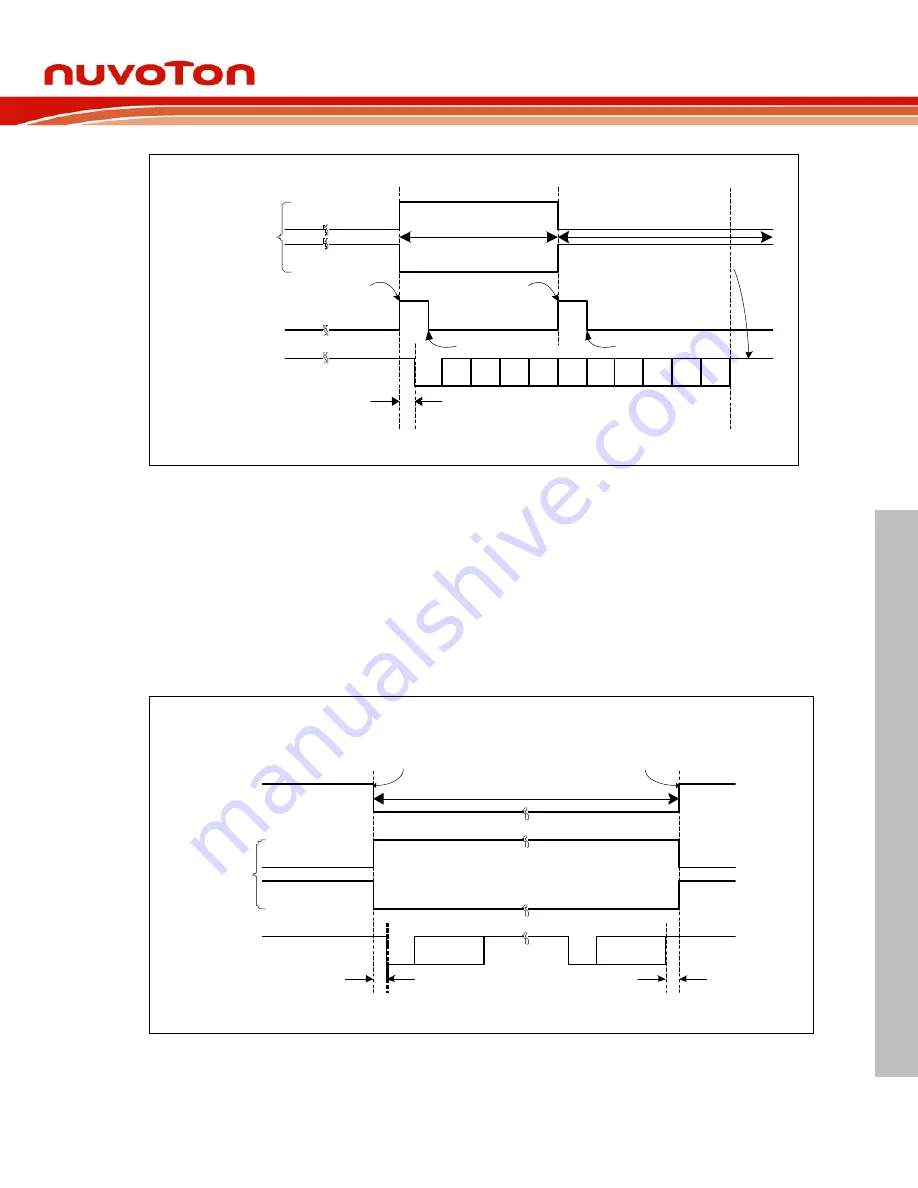

UART0_nCTS pin

input

Active

UART0_nCTS pin input status of UART function mode

D0

D1

D2

D3

D4

D5

D6

D7

P

Start

bit

Stop

bit

UART0_TXD pin

output

MODEMINT interrupt

Clear by softwave

Clear by softwave

Idle

Idle

TX output

delay

(default)

CTSSTS

(UART_MODEMSTS[4])

CTSACTLV=0

CTSACTLV=1

CTSDETF

MODEMINT interrupt

TX stop

Inactive

Figure 6.12-12 UART nCTS Auto-Flow Control Enabled

As shown in Figure 6.12-13, in UART nRTS auto-flow control mode (ATORTSEN

(UART_INTEN[12])=1), the nRTS internal signal is controlled by UART FIFO controller with

RTSTRGLV(UART_FIFO[19:16]) trigger level.

Setting RTSACTLV (UART_MODEM[9]) can control the nRTS pin output is inverse or non-inverse

from nRTS signal. User can read the RTSSTS (UART_MODEM[13]) bit to get real nRTS pin output

voltage logic status.

RTSACTLV = 0

nRTS Signal

(internal signal)

Active

Byte(i)

Byte (i +n)

Start

bit

UART0_RXD pin

input

(from external)

nRTS inactive

delay

External

delay

Start

bit

The Bytes

Number Stored

In FIFO

<

The Bytes Number

Stored In FIFO

=

UART0_nRTS pin output status of UART function mode, nRTS auto - flow control enabled

RTSTRGLV

(UART_FIFO[19:16])

RTSTRGLV

(UART_FIFO[19:16])

RTSSTS

(UART_MODEM[13])

UART0_nRTS pin

output

RTSACTLV = 1

(Default)

Figure 6.12-13 UART nRTS Auto-Flow Control Enabled

As shown in Figure 6.12-14, in software mode (ATORTSEN(UART_INTEN[12])=0), the nRTS flow