ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

614

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

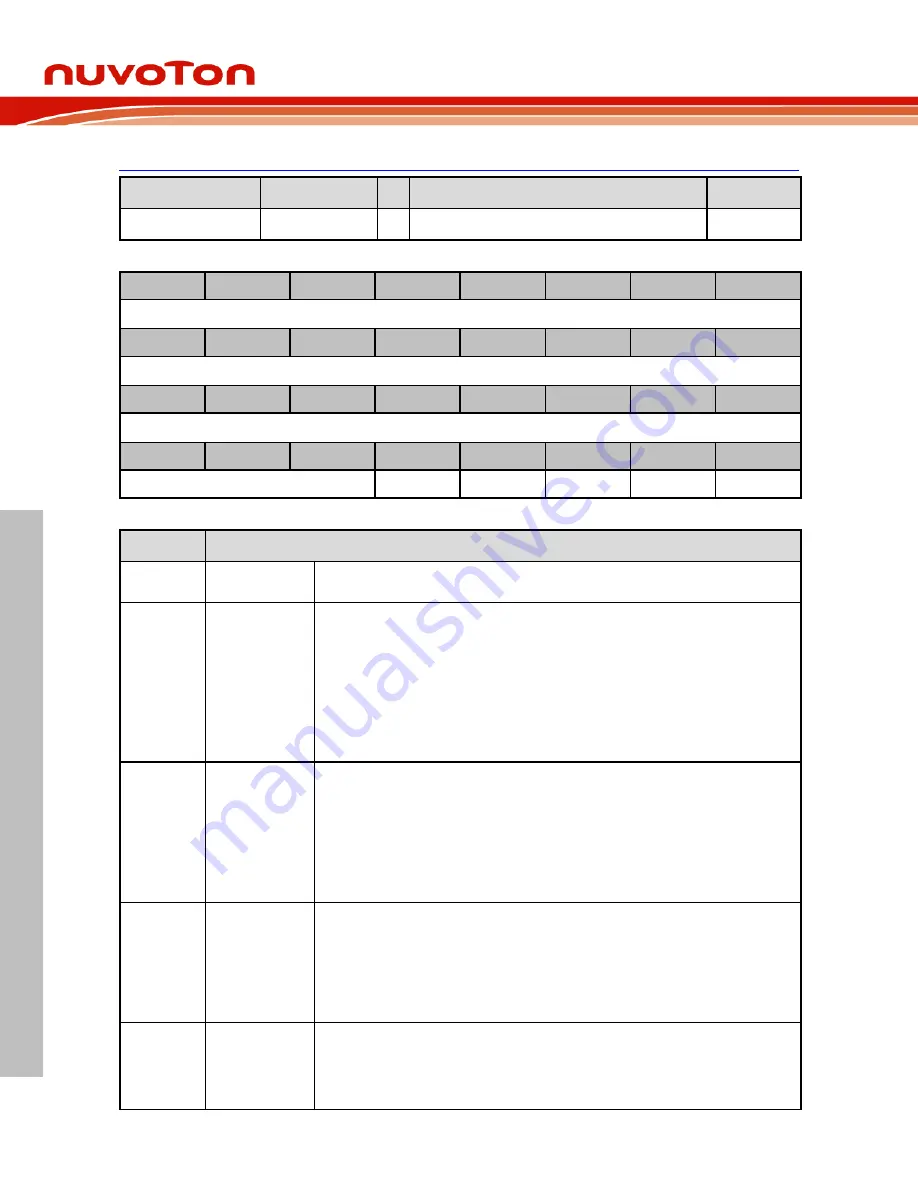

UART Wake-up Status Register (UART_WKSTS)

Register

Offset

R/W Description

Reset Value

UART_WKSTS

U0x44

R/W UART Wake-up Status Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Reserved

TOUTWKF

RS485WKF

RFRTWKF

DATWKF

CTSWKF

Bits

Description

[31:5]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[4]

TOUTWKF

RX FIFO Threshold Time-out Wake-up Flag

This bit is set indicating system wake-up from a RX FIFO Threshold Time-out event

0 = Chip stays in power-down state.

1 = Chip wake-up from RX FIFO Threshold Time-out event.

wake-up.

Note1:

If WKTOUTEN (UART_WKCTL[4]) is enabled, the RX FIFO threshold time-out

wake-up will set TOUTWKF bit to ‘1’.

Note2:

This bit can be cleared by writing ‘1’ to it.

[3]

RS485WKF

RS-485 Address Match (AAD Mode) Wake-up Flag

This bit is set if chip wake-up from power-down state by RS-485 Address Match (AAD mode).

0 = Chip stays in power-down state.

1 = Chip wake-up from power-down state by RS-485 Address Match (AAD mode) wake-up.

Note1:

If WKRS485EN (UART_WKCTL[3]) is enabled, the RS-485 Address Match (AAD

mode) wake-up cause this bit is set to ‘1’.

Note2:

This bit can be cleared by writing ‘1’ to it.

[2]

RFRTWKF

This bit is set if chip wake-up from power-down state by RX FIFO reached threshold

wake-up .

0 = Chip stays in power-down state.

1 = Chip wake-up from power-down state by RX FIFO Reached Threshold wake-up.

Note1:

If WKRFRTEN (UART_WKCTL[2]) is enabled, the RX FIFO Reached Threshold

wake-up cause this bit is set to ‘1’.

[1]

DATWKF

Incoming Data Wake-up Flag

This bit is set if chip wake-up from power-down state by data wake-up.

0 = Chip stays in power-down state.

1 = Chip wake-up from power-down state by Incoming Data wake-up.