ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

619

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

PC.14

MFP2

PD.1

MFP3

PD.9

MFP4

PD.15

MFP3

I2C0_SMBAL

PA.12

MFP1

I2C0_SMBSUS

PA.11

MFP1

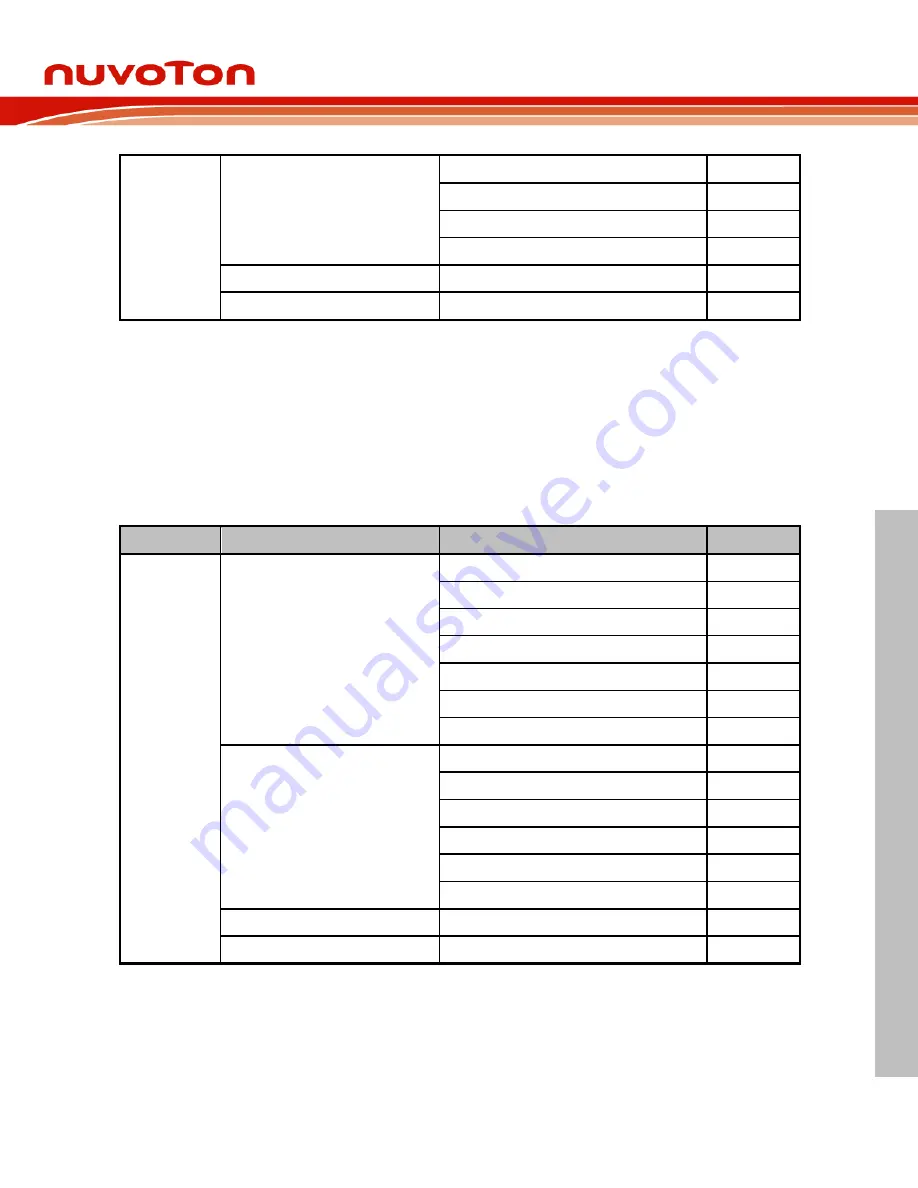

6.13.4.2 I2C1 Basic Configurations

Clock source configuration

–

Enable I2C1 peripheral clock in I2C1CKEN (CLK_APBCLK0[9]).

Reset configuration

–

Reset I2C1 controller in I2C1RST (SYS_IPRST1[9]).

Pin configuration

Group

Pin Name

GPIO

MFP

I2C1

I2C1_SCL

PA.13

MFP4

PB.6

MFP4

PC.0

MFP1

PD.0

MFP2

PD.2

MFP4

PD.8

MFP3

PD.14

MFP5

I2C1_SDA

PA.14

MFP4

PB.5

MFP4

PC.1

MFP1

PD.1

MFP2

PD.9

MFP3

PD.15

MFP5

I2C1_SMBAL

PC.3

MFP1

I2C1_SMBSUS

PC.2

MFP1

6.13.5 Functional Description

On I

2

C bus, data is transferred between a Master and a Slave. Data bits transfer on the SCL and

SDA lines are synchronously on a byte-by-byte basis. Each data byte is 8-bit long. There is one

SCL clock pulse for each data bit with the MSB being transmitted first, and an acknowledge bit

follows each transferred byte. Each bit is sampled during the high period of SCL; therefore, the SDA