ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

64

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

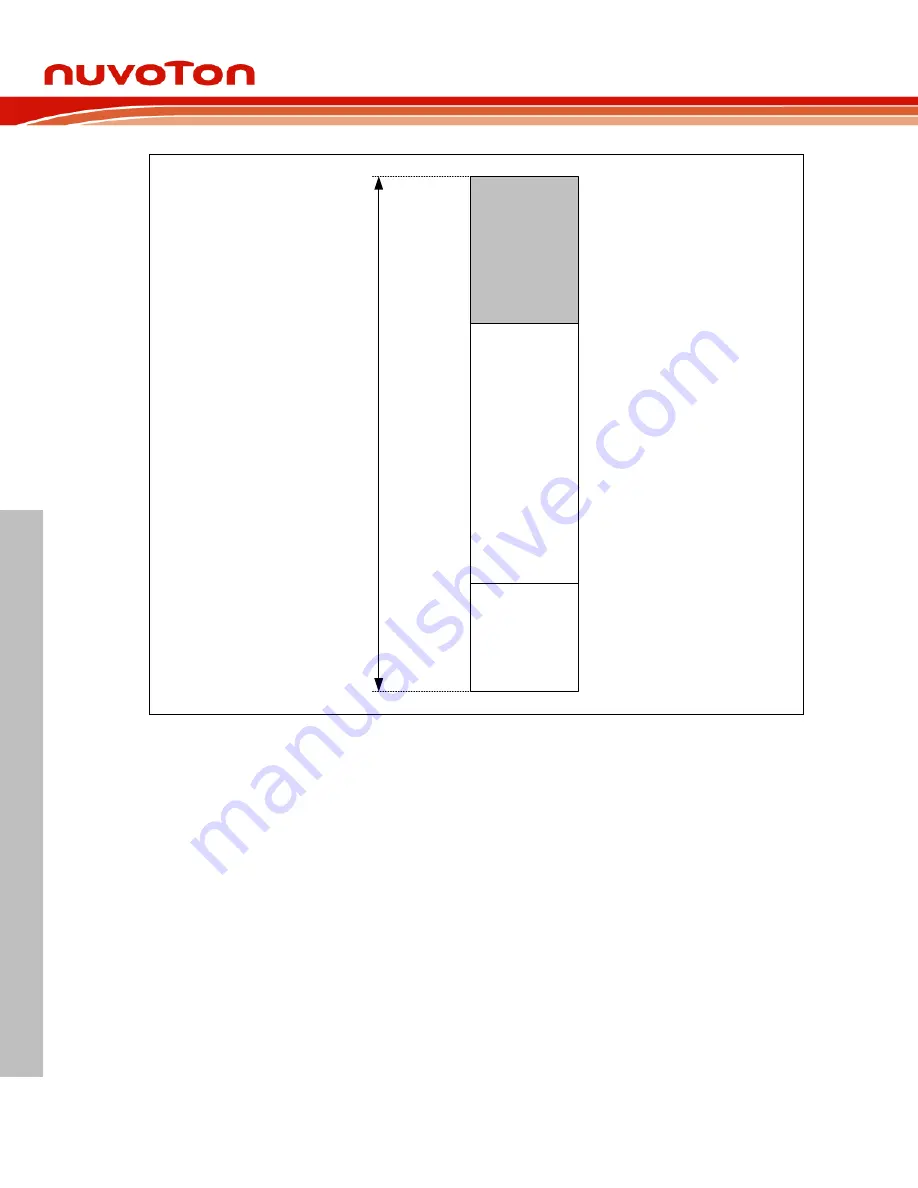

512

MB

32 KB

SRAM

0x2000_0000

Reserved

0x3FFF_FFFF

0x2000_7FFF

0x2000_8000

160 KB

SRAM

0x2003_0000

0x2002_FFFF

Figure 6.2-7 SRAM Memory Organization

SRAM address from 0x2000_0000 to 0x2000_7FFF has byte parity error check function. When

CPU is accessing SRAM address from 0x2000_0000 to 0x2000_7FFF the parity error checking

mechanism is operating dynamically. If parity error occurrs, the PERRIF (SYS_SRAM_STATUS[0])

will be asserted to 1 and the SYS_SRAM_ERRADDR register will record the address with parity

error. Chip will enter interrupt when SRAM parity error occurs if PERRIEN (SYS_SRAM_INTCTL[0])

is set to 1. When SRAM parity error occurs, chip will stop detecting SRAM parity errors until user

writes 1 to clear the PERRIF(SYS_SRAM_STATUS[0]) bit.

6.2.9

HIRC Auto Trim

This chip supports auto-trim function: the HIRC trim, according to the accurate LXT (32.768 kHz

crystal oscillator) or USB SOF (Start-Of-Frame), automatically gets accurate HIRC output frequency,

0.25 % deviation within all temperature ranges.

For instance, the system needs an accurate 49.152 MHz or 48 MHz clock. In such case, if neither

using PLL as the system clock source nor soldering 32.768 kHz crystal in system, user has to set

REFCKSEL (SYS_IRCTCTL[10] reference clock selection) to “1”,

set FREQSEL

(SYS_IRCTCTL[1:0] trim frequency selection) to “10” or “11”, and the auto-trim function will be

enabled. Interrupt status bit FREQLOCK (SYS_IRCTISTS[8] HIRC frequency lock status) “1”

indicates the HIRC output frequency is accurate within 0.25% deviation.