ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

650

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

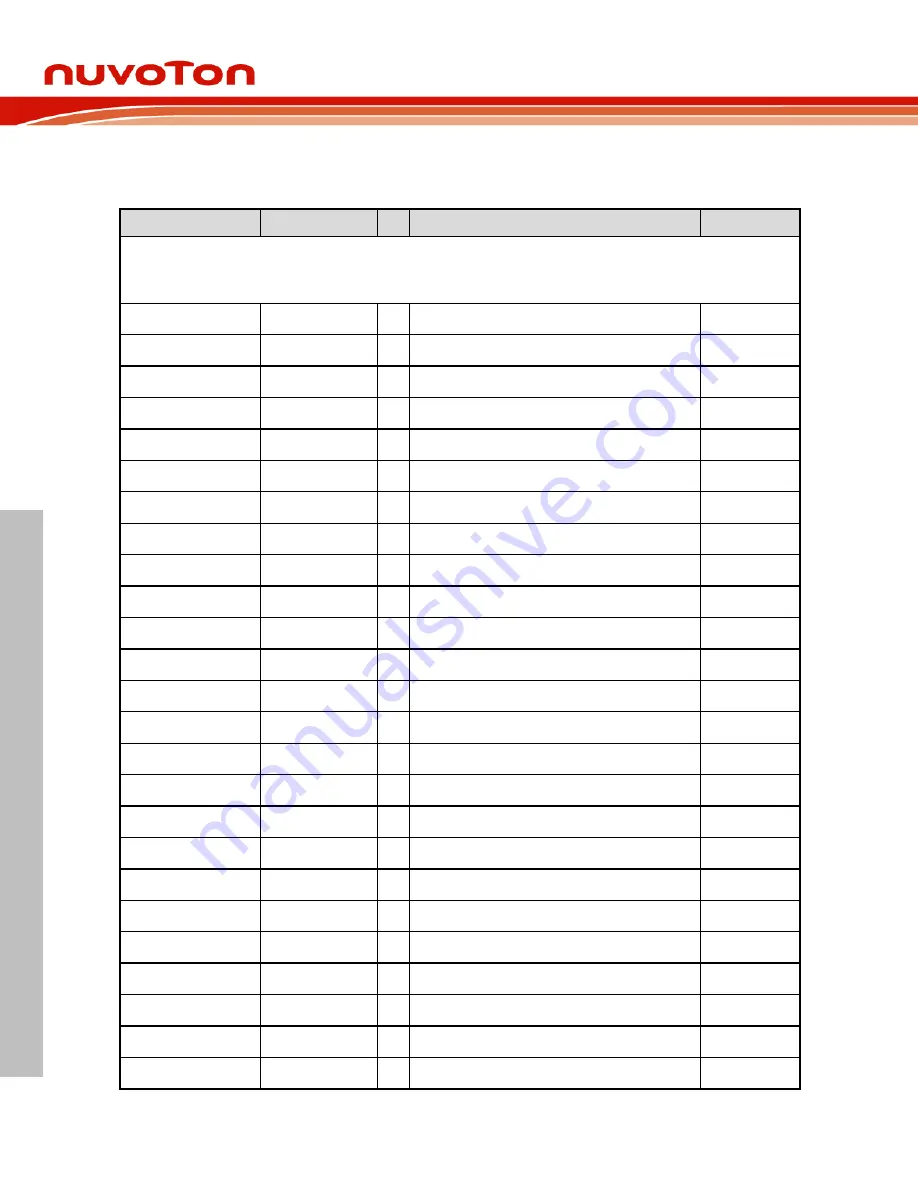

6.13.6 Register Map

R:

read only,

W:

write only,

R/W:

both read and write

Register

Offset

R/W Description

Reset Value

I

2

C Base Address:

I2Cn_BA = 0x400 (0x1000 *n)

n= 0,1

I2C_CTL

0x00

R/W I

2

C Control Register 0

0x0000_0000

I2C_ADDR0

0x04

R/W I

2

C Slave Address Register0

0x0000_0000

I2C_DAT

0x08

R/W I

2

C Data Register

0x0000_0000

I2C_STATUS

0x0C

R

I

2

C Status Register 0

0x0000_00F8

I2C_CLKDIV

0x10

R/W I

2

C Clock Divided Register

0x0000_0000

I2C_TOCTL

0x14

R/W I

2

C Time-out Control Register

0x0000_0000

I2C_ADDR1

0x18

R/W I

2

C Slave Address Register1

0x0000_0000

I2C_ADDR2

0x1C

R/W I

2

C Slave Address Register2

0x0000_0000

I2C_ADDR3

0x20

R/W I

2

C Slave Address Register3

0x0000_0000

I2C_ADDRMSK0

0x24

R/W I

2

C Slave Address Mask Register0

0x0000_0000

I2C_ADDRMSK1

0x28

R/W I

2

C Slave Address Mask Register1

0x0000_0000

I2C_ADDRMSK2

0x2C

R/W I

2

C Slave Address Mask Register2

0x0000_0000

I2C_ADDRMSK3

0x30

R/W I

2

C Slave Address Mask Register3

0x0000_0000

I2C_WKCTL

0x3C

R/W I

2

C Wake-up Control Register

0x0000_0000

I2C_WKSTS

0x40

R/W I

2

C Wake-up Status Register

0x0000_0000

I2C_CTL1

0x44

R/W I

2

C Control Register 1

0x0000_0000

I2C_STATUS1

0x48

R/W I

2

C Status Register 1

0x0000_0000

I2C_TMCTL

0x4C

R/W I2C Timing Configure Control Register

0x0000_0000

I2C_BUSCTL

0x50

R/W I

2

C Bus Management Control Register

0x0000_0000

I2C_BUSTCTL

0x54

R/W I

2

C Bus Management Timer Control Register

0x0000_0000

I2C_BUSSTS

0x58

R/W I

2

C Bus Management Status Register

0x0000_0000

I2C_PKTSIZE

0x5C

R/W I

2

C Packet Error Checking Byte Number Register

0x0000_0000

I2C_PKTCRC

0x60

R

I

2

C Packet Error Checking Byte Value Register

0x0000_0000

I2C_BUSTOUT

0x64

R/W I

2

C Bus Management Timer Register

0x0000_0005

I2C_CLKTOUT

0x68

R/W I

2

C Bus Management Clock Low Timer Register

0x0000_0005

Note: