ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

674

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

6.14 Serial Peripheral Interface (SPI)

6.14.1 Overview

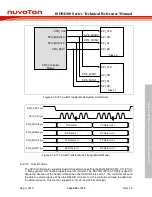

The Serial Peripheral Interface (SPI) is a synchronous serial data communication interface. SPI

devices communicate in full duplex mode using a master-slave architecture. The single master and

the slave(s) communicate bi-directionally through a 4-wire interface.

The ISD94100 series contains up to three sets of SPI controllers which perform serial-to-parallel

conversion when receiving data from a peripheral device, and parallel-to-serial conversion when

transmitting data to a peripheral device. Each SPI controller can be configured as a master or a

slave device.

SPI0 controller supports 2-bit Transfer mode to perform full-duplex 2-bit data transfer and also

supports Dual and Quad I/O Transfer mode. SPI1 and SPI2 controllers support I

2

S mode to connect

external audio CODEC. Each SPI controller supports the PDMA function to access the data buffer.

6.14.2 Features

SPI Mode

Up to three sets of SPI controllers

Supports Master or Slave mode operation

Master mode up to 25 MHz and Slave mode up to 25 MHz (when chip works at VDD =

2.7~3.6V)

Supports 2-bit Transfer mode (SPI0 Only)

Supports Dual and Quad I/O Transfer mode (SPI0 Only)

Configurable bit length of a transaction word from 8 to 32-bit

Provides separate 4-/8-level depth transmit and receive FIFO buffers

Supports MSB first or LSB first transfer sequence

Supports Byte Reorder function

Supports Byte or Word Suspend mode

Supports PDMA transfer

Supports 3-Wire, no slave selection signal, bi-direction interface (SPI0 Only)

Supports one data channel half-duplex transfer

Support receive-only mode

I

2

S Mode (for SPI1~SPI2)

Supports Master or Slave

Capable of handling 8-, 16-, 24- and 32-bit word sizes

Each provides two 4-level FIFO data buffers, one for transmitting and the other for receiving

Supports monaural and stereo audio data

Supports PCM mode A, PCM mode B, I

2

S and MSB justified data format

Supports two PDMA requests, one for transmitting and the other for receiving