ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

676

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

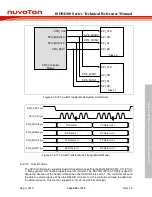

6.14.3 Block Diagram

APB

Interface

Control

Status / Control

Registers

Core Logic

8-Level TX

FIFO Buffer

8-Level RX

FIFO Buffer

TX Shift

Register

RX Shift

Register

4-Bit

Skew

Buffer

4-Bit

Skew

Buffer

SPI0_CLK

DMA

Interface

Control

SPI0_MOSI0

SPI0_MISO0

SPI0_SS0

Peripheral clock

SPI0_MOSI1

SPI0_MISO1

Note: SPI0_MOSI1 and SPI0_MISO1 are only available in 2-Bit Transfer mode or Quad I/O mode

SPI0_SS1

Figure 6.14-1 SPI Block Diagram (SPI0)

APB

Interface

Control

Status / Control

Registers

Core Logic

4-Level TX

FIFO Buffer

4-Level RX

FIFO Buffer

TX Shift

Register

RX Shift

Register

4-Bit

Skew

Buffer

4-Bit

Skew

Buffer

SPIx_CLK (I2Sn_BCLK)

DMA

Interface

Control

SPIx_MOSI (I2Sn_DO)

SPIx_MISO (I2Sn_DI)

SPIx_SS (I2Sn_LRCLK)

Peripheral clock

Note: x = 1, 2

SPIx_I2SMCLK

Figure 6.14-2 SPI Block Diagram (SPI1/2)