ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

680

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

SPIx_MOSI

SPI master output or slave input pin

I

2

S data output pin (I2Sx_DO)

SPIx_I2SMCLK

Not available

I

2

S Master clock output pin

Note:

When using the I2S function in SPI1 and SPI2, please enable schmitt trigger function

(Px_SMTEN) on corresponding pins.

Table 6.14-3 SPI/I2S Interface Controller Pin Description (SPI1~SPI2)

6.14.5 Functional Description

6.14.5.1 Terminology

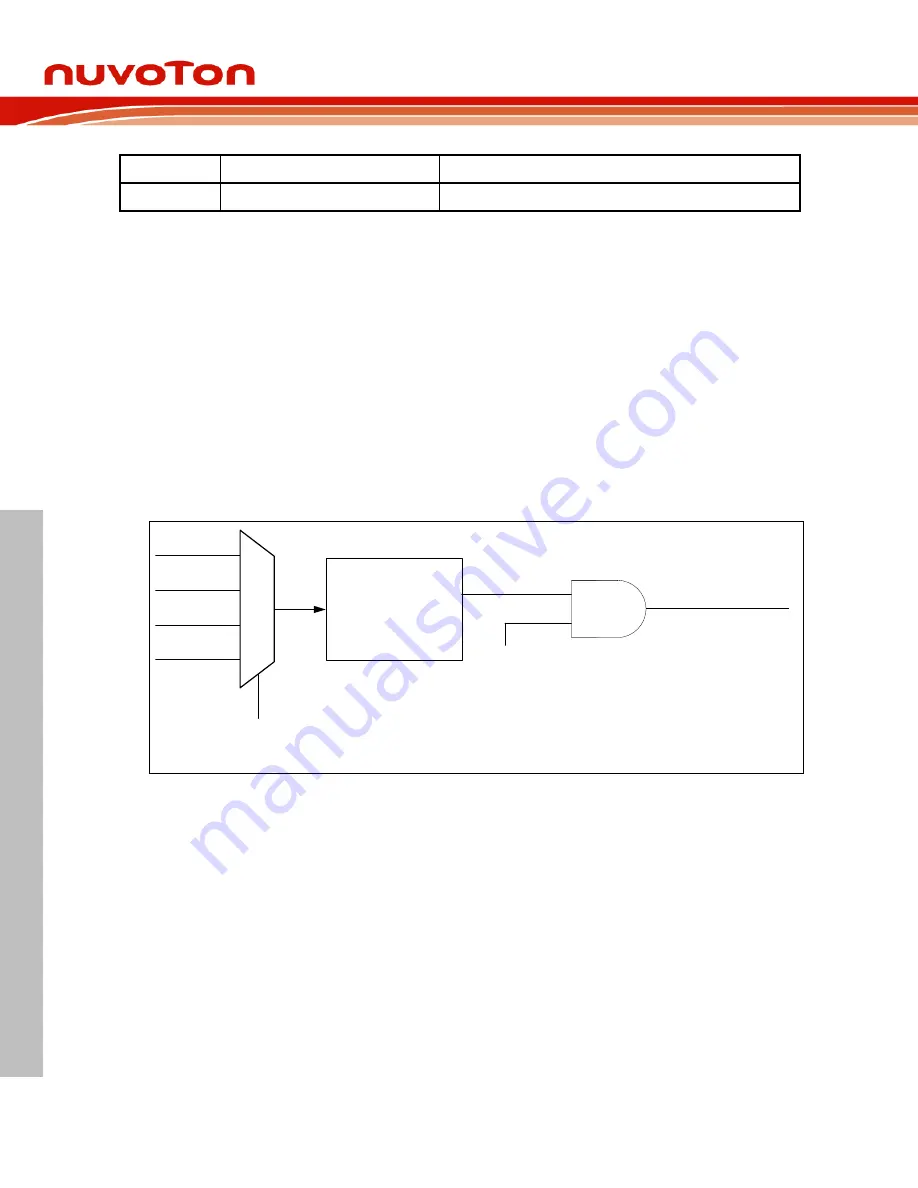

SPI Peripheral Clock and SPI Bus Clock

The SPI controller needs the peripheral clock to drive the SPI logic unit to perform the data transfer.

The peripheral clock rate is determined by the settings of clock divider (SPIn_CLKDIV) and the

clock source which can be HXT, PLL, PCLK or HIRC. SPInSEL of CLK_CLKSEL2 register

determines the clock source of the peripheral clock. The DIVIDER (SPIn_CLKDIV[8:0]) setting

determines the divisor of the clock rate calculation.

SPIn Clock Divider

(SPIn_CLKDIV[8:0]/

SPIn_I2SCLK[17:8])

SPInSEL

HXT

PLL

PCLK

HIRC

SPInCKEN

SPIn Peripheral

Clock

Note: n = 0, 1, 2

SPI0SEL = CLK_CLKSEL2[3:2] SPI0CKEN = CLK_APBCLK0[12]

SPI1SEL = CLK_CLKSEL2[5:4] SPI1CKEN = CLK_APBCLK0[13]

SPI2SEL = CLK_CLKSEL2[7:6] SPI2CKEN = CLK_APBCLK0[14]

00

01

10

11

Figure 6.14-4 SPI Peripheral Clock

In Master mode, the frequency of the SPI bus clock is equal to the peripheral clock rate. In general,

the SPI bus clock is denoted as SPI clock. In Slave mode, the SPI bus clock is provided by a master

device. The frequency of SPI peripheral clock cannot be faster than the system clock rate

regardless of Master or Slave mode. If the clock source of peripheral clock is not system clock, the

frequency of SPI peripheral clock shall be slower than the system clock frequency regardless of

Master or Slave mode.

In I

2

S mode, the peripheral clock rate is equal to I

2

S bit clock rate determined by SPIn_I2SCLK

register.

Master/Slave mode

The SPI controllers can be set as Master or Slave mode by setting the SLAVE (SPIn_CTL[18]) to

communicate with the off-chip SPI slave or master device. The HALFDPX (SPIn_CTL[14]) can be