ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

692

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

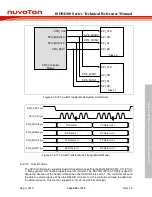

SPI0_SS0/1 pin

7 6 5 4 3 2 1 0

SPI0_CLK pin

SPI0_MOSI0 pin

SPI0_MISO0 pin

QUADIOEN

C 8 4 0 C 8 4 0

D 9 5 1 D 9 5 1

C 8 4 0 C 8 4 0

D 9 5 1 D 9 5 1

DATDIR

Master output

Slave input

Master input

Slave output

Input

Input

SPI0_MOSI1 pin

SPI0_MISO1 pin

E A 6 2 E A 6 2

F B 7 3 F B 7 3

E A 6 2 E A 6 2

F B 7 3 F B 7 3

Master output

Slave input

Master input

Slave output

Input

Input

Figure 6.14-21 Bit Sequence of Quad Input Mode

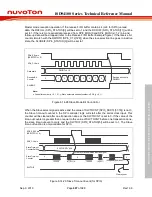

6.14.5.11 FIFO Buffer Operation

The SPI controllers equip with four 32-bit wide transmit and receive FIFO buffers. The data stored

in the transmit FIFO buffer will be read and sent out by the transmission control logic. If the transmit

FIFO buffer is full, the TXFULL (SPIn_STATUS[17]) will be set to 1. When the SPI transmission

logic unit draws out the last datum of the transmit FIFO buffer, so that the transmit FIFO buffer is

empty, the TXEMPTY (SPIn_STATUS[16]) will be set to 1. Notice that the TXEMPTY

(SPIn_STATUS[16]) flag is set to 1 while the last transaction is still in progress. In Master mode,

the BUSY (SPIn_STATUS[0]) is set to 1 when the FIFO buffer is written any data or there is any

transaction on the SPI bus. (e.g. the slave selection signal is active and the SPI controller is

receiving data in Slave mode). It will set to 0 when the transmit FIFO is empty and the current

transaction has done. Thus, the status of BUSY (SPIn_STATUS[0]) should be checked by software

to make sure whether the SPI is in idle or not.

The receive control logic will store the SPI input data into the receive FIFO buffer. There are FIFO

related status bits, like RXEMPTY (SPIn_STATUS[8]) and RXFULL (SPIn_STATUS[9]), to indicate

the current status of RX FIFO buffer.

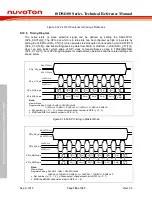

The transmitting and receiving threshold can be configured by setting TXTH

(SPIn_FIFOCTL[30:28]) and RXTH (SPIn_FIFOCTL[26:24]). When the count of valid data stored

in transmit FIFO buffer is less than or equal to TXTH (SPIn_FIFOCTL[30:28]) setting, TXTHIF

(SPIn_STATUS[18]) will be set to 1. When the count of valid data stored in receive FIFO buffer is

larger than RXTH (SPIn_FIFOCTL[26:24]) setting, RXTHIF (SPIn_STATUS[10]) will be set to 1.