ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

695

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

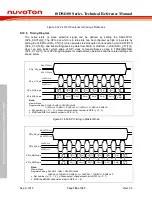

RXEMPTY = 1

RXEMPTY = 1

RXEMPTY = 1

b31|b30...b1|b0

b0

Data 0

RXEMPTY = 0

Example 1

SPI0

DWIDTH =0

LSB = 1

RX Skew Buffer

RX Shift Register

RX FIFO Buffer

H/W Load

Skew Buffer

into Shift

Register

b1

……………

.b0

b32

…………

..b32

b33

1. H/W load Shift

Register into RX

FIFO

2. H/W Load

Skew Buffer into

Shift Register

RXEMPTY = 1

RXEMPTY = 0

RXEMPTY = 0

RXFULL = 1

Example 2

SPI0

DWIDTH =0

LSB = 1

Data 1

Data N

b31|b30...b1|b0

Data 0

1. H/W load

Shift Register

into RX FIFO

2. H/W Load

Skew Buffer

into Shift

Register

Data 9

1. Read Out by

User

2. Repeat

Receive Data

into RX FIFO

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

Data 8

RXEMPTY = 0

RXFULL = 1

RXOVIF = 1

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

Data 8

RX Shift Register

RX FIFO Buffer

H/W Load 32

bits into

Shift Register

The 9

th

Data

can not load

into RX FIFO

Buffer when

RX FIFO Full

Figure 6.14-24 Receive FIFO Buffer Example

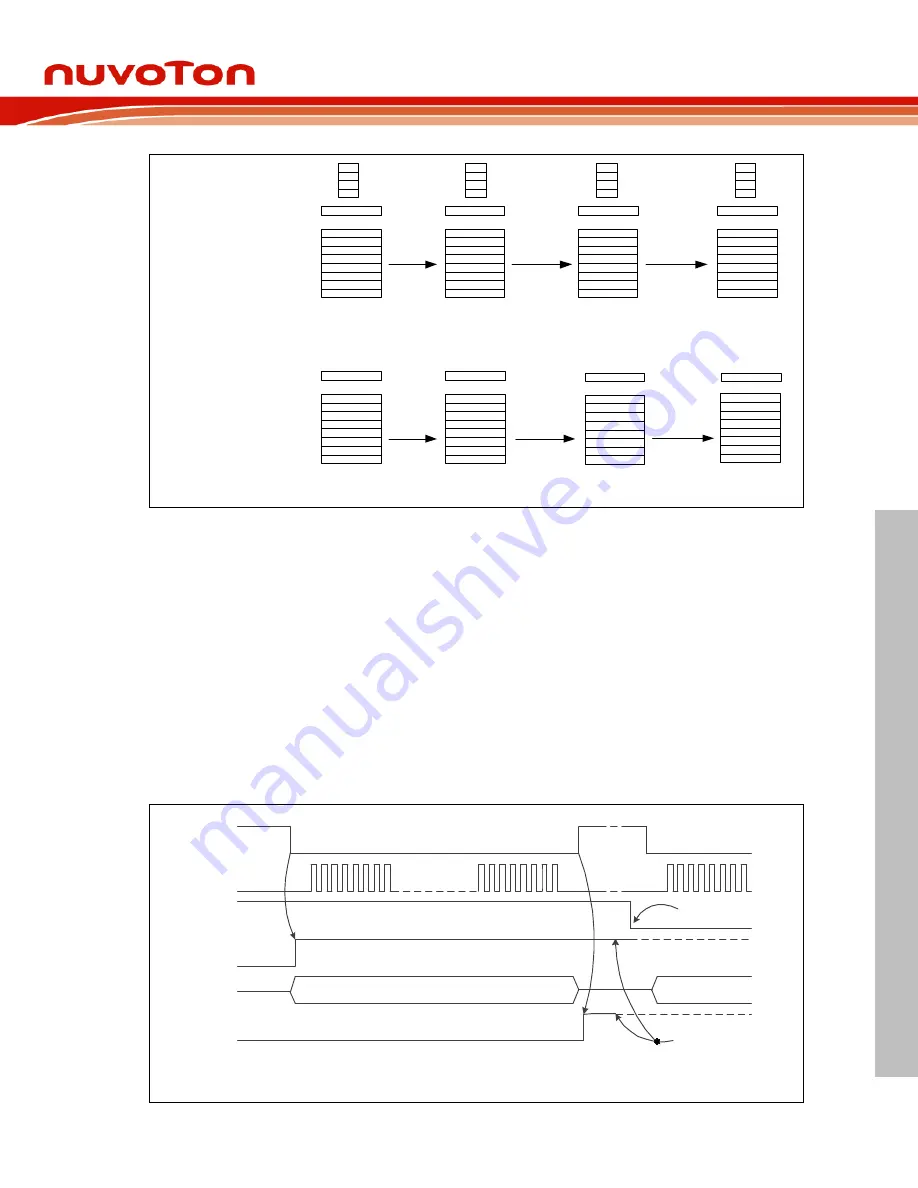

In Slave mode, during transmission operation, when data is written to the SPIn_TX register by

software, the data will be loaded into transmit FIFO buffer and the TXEMPTY (SPIn_STATUS[16])

will be set to 0. The transmission will start when the slave device receives clock signal from master.

Data can be written to SPIn_TX register as long as the TXFULL (SPIn_STATUS[17]) is 0. After all

data have been drawn out by the SPI transmission logic unit and the SPIn_TX register is not

updated by software, the TXEMPTY (SPIn_STATUS[16]) will be set to 1.

If there is no any data written to the SPIn_TX register, the transmit underflow interrupt flag, TXUFIF

(SPIn_STATUS[19]) will be set to 1 when the slave selection signal is active. The output data will

be held by TXUFPOL (SPIn_FIFOCTL[6]) setting during this transfer until the slave selection signal

goes to inactive state. When the transmit underflow event occurs, the slave under run interrupt flag,

SLVURIF (SPIn_STATUS[7]), will be set to 1 as slave selection pin goes to inactive state.

SPIx_SSy pin

SPIx_CLK pin

SPIx_MISOz pin

TXEMPTY

SLVURIF

TXUFPOL

TXUFIF

Data 0 is written

into FIFO Buffer

Data 0

Read & Clear by

User

Note:

x: Controller number (x = 0, 1, 2), y: Slave selection pin channel number in SPI0 (y = 0, 1),

z: MOSI and MISO pin channel number in SPI0 (z = 0)