ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

736

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

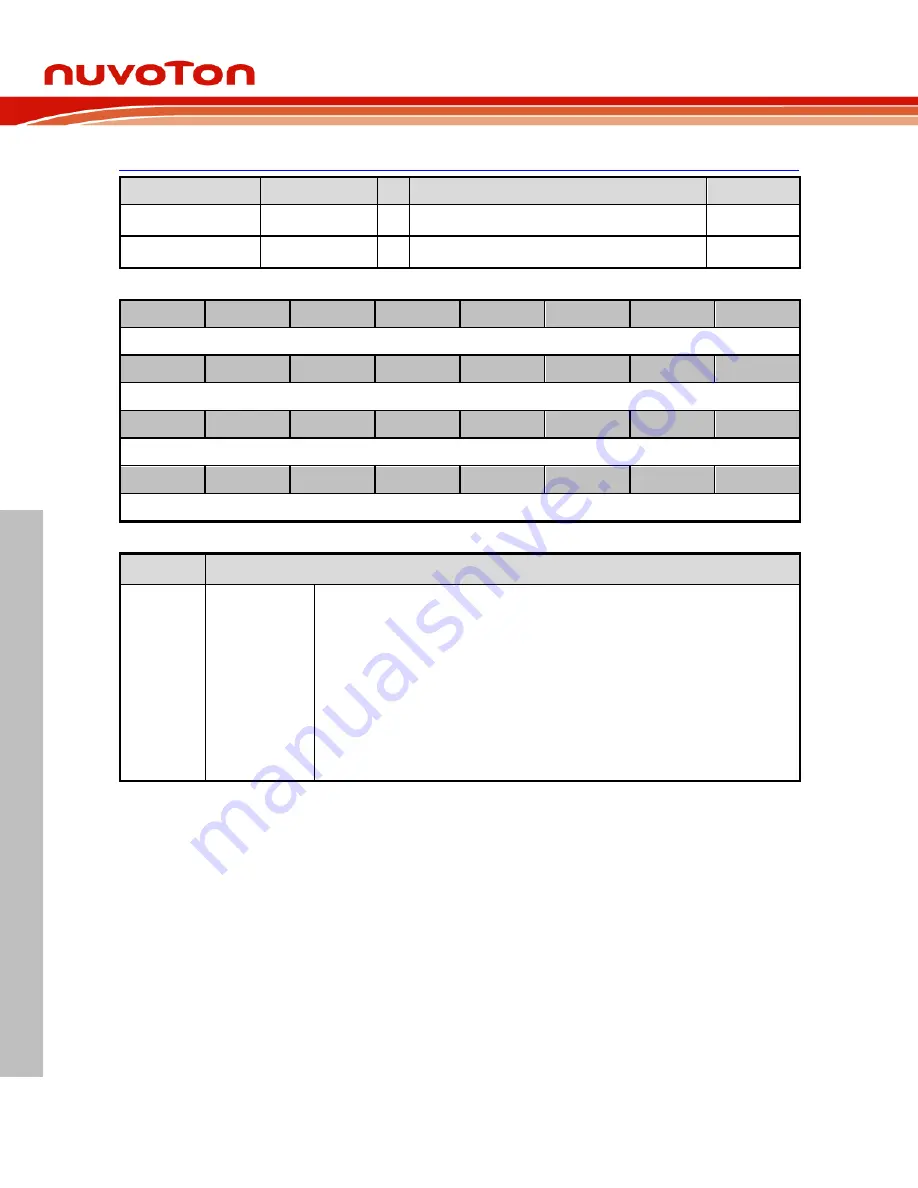

SPI Data Transmit Register (SPIn_TX)

Register

Offset

R/W Description

Reset Value

SPI1_TX

0x20

W

SPI1 Data Transmit Register

0x0000_0000

SPI2_TX

0x20

W

SPI2 Data Transmit Register

0x0000_0000

31

30

29

28

27

26

25

24

TX

23

22

21

20

19

18

17

16

TX

15

14

13

12

11

10

9

8

TX

7

6

5

4

3

2

1

0

TX

Bits

Description

[31:0]

TX

Data Transmit Register

The data transmit registers pass through the transmitted data into the 4-level transmit FIFO

buffers. The number of valid bits depends on the setting of DWIDTH (SPIn_CTL[12:8]) in

SPI mode or WDWIDTH (SPIn_I2SCTL[5:4]) in I

2

S mode.

In SPI mode, if DWIDTH is set to 0x08, the bits TX[7:0] will be transmitted. If DWIDTH is set

to 0x00 , the SPI controller will perform a 32-bit transfer.

In I

2

S mode, if WDWIDTH (SPIn_I2SCTL[5:4]) is set to 0x2, the data width of audio channel

is 24-bit and corresponding to TX[23:0]. If WDWIDTH is set as 0x0, 0x1, or 0x3, all bits of

this field are valid and referred to the data arrangement in I

2

S mode FIFO operation section

Note:

In Master mode, SPI controller will start to transfer the SPI bus clock after 1 APB clock

and 6 peripheral clock cycles after user writes to this register.