ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

755

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

6.16 Enhanced 12-bit Analog-to-Digital Converter (EADC)

6.16.1 Overview

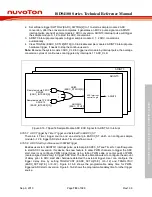

The ISD94100 series contains one 12-bit successive approximation analog-to-digital converter

(SAR ADC converter) with 13 external input channels. The ADC converter can be started by

software trigger, PWM0 triggers, timer0~3 overflow pulse triggers, ADINT0, ADINT1 interrupt EOC

(End of conversion) pulse trigger and external pin (EADC0_ST) input signal.

6.16.2 Features

Analog input voltage range: 0~AV

DD

.

Reference voltage from AVDD.

12-bit resolution and 9-bit accuracy is guaranteed.

Up to 13 single-end analog external input channels.

Four ADC interrupts (ADINT0~3) with individual interrupt vector addresses.

Maximum ADC clock frequency is 60 MHz.

Up to 2 MSPS conversion rate.

Configurable ADC internal sampling time.

12-bit, 10-bit, 8-bit, 6-bit configurable resolution.

Supports calibration capability when EADC enabled.

Supports three power saving modes:

Deep Power-down mode

Power-down mode.

Standby mode.

Up to 13 sample modules

Each of sample modules which is configurable for ADC converter channel

EADC_CH0~12 and trigger source.

Double buffer for sample control logic module 0~3

Configurable sampling time for each sample module.

Conversion results are held in 13 data registers with valid and overrun indicators.

An ADC conversion can be started by:

Write 1 to SWTRGn (EADC_SWTRG[n] , n = 0~12)

External pin EADC0_ST

Timer0~3 overflow pulse triggers

ADINT0 and ADINT1 interrupt EOC (End of conversion) pulse triggers

PWM triggers

Supports PDMA transfer