ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

761

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

Note:

If the interval between next conversion is more than 100 us, ADC would enter idle state

automatically. User needs to execute a dummy conversion before normal operation. In other words,

the first conversion result is incorrect when ADC is in idle state.

6.16.5.3 ADC Conversion Priority

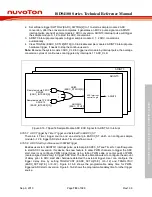

There is a priority group converter for determining the conversion order when multiple sample

module trigger flags are set at the same time.

Sample module with lower number has higher priority than the higher number sample module, The

priority of sample module is shown as Figure 6.16-6. When more than one Sample Module are

triggered at the same time, the Sample Module with lower number will start to convert first. The

other Sample Module will be in the queue and the corresponding pending flag

STPF(EADC_PENDSTS[n], n=0~12) are set to 1 by HW. After the Sample Module finish the

conversion, STPF(EADC_PENDSTS[n], n=0~12) will be set to 0 automatically. If the Sample

Module which is in the queue is triggered once more, the corresponding Overrun Flag

SPOVF(EADC_OVSTS[n], n=0~12) will be set to 1 by HW.

For example, the Sample Module 0, 2, 3, 5 are triggered simultaneously. The input channel of

Sample Module 0 will be converted first. Sample Module 2, 3, 5 will be suspended and STPF

(EADC_PENDSTS[2], EADC_PENDSTS [3], EADC_PENDSTS [5]) will be set to 1. If Sample

Module 5 is trigger once more in the same time, SPOVF(EADC_OVSTS[5]) will be set to 1.

Sample

Module 0

Sample

Module 1

Sample

Module 2

Sample

Module

12

SAMPLE Priority

Sample module 0 has highest priority, sample module 12 has lowest priority for

ADC converter

Figure 6.16-6 Sample module Conversion Priority Arbitrator Diagram