ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

786

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

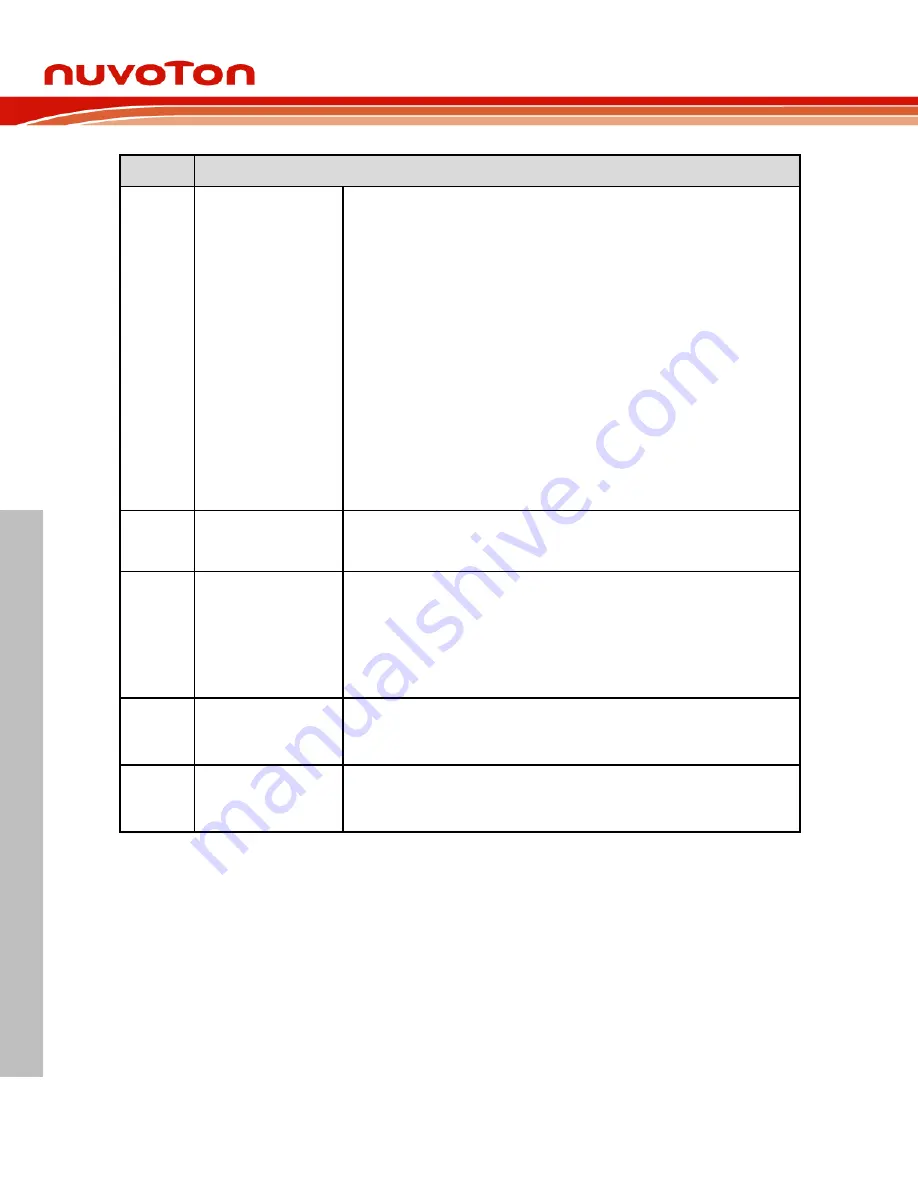

Bits

Description

[20:16]

TRGSEL

ADC Sample Module Start of Conversion Trigger Source Selection

0H = Disable trigger.

1H = External trigger from EADC0_ST pin input.

2H = ADC ADINT0 interrupt EOC pulse trigger.

3H = ADC ADINT1 interrupt EOC pulse trigger.

4H = Timer0 overflow pulse trigger.

5H = Timer1 overflow pulse trigger.

6H = Timer2 overflow pulse trigger.

7H = Timer3 overflow pulse trigger.

8H = PWM0TG0.

9H = PWM0TG1.

AH = PWM0TG2.

BH = PWM0TG3.

CH = PWM0TG4.

DH = PWM0TG5.

Other = Reserved. Do not use.

[15:8]

TRGDLYCNT

ADC Sample Module Start of Conversion Trigger Delay Time

Trigger delay time = TRGDLYCNT x ADC_CLK x n (n=1,2,4,16 from TRGDLYDIV

setting).

[7:6]

TRGDLYDIV

ADC Sample Module Start of Conversion Trigger Delay Clock Divider Selection

Trigger delay clock frequency:

00 = ADC_CLK/1.

01 = ADC_CLK/2.

10 = ADC_CLK/4.

11 = ADC_CLK/16.

[5]

EXTFEN

ADC External Trigger Falling Edge Enable Bit

0 = Falling edge Disabled when ADC selects EADC0_ST as trigger source.

1 = Falling edge Enabled when ADC selects EADC0_ST as trigger source.

[4]

EXTREN

ADC External Trigger Rising Edge Enable Bit

0 = Rising edge Disabled when ADC selects EADC0_ST as trigger source.

1 = Rising edge Enabled when ADC selects EADC0_ST as trigger source.