ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

802

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

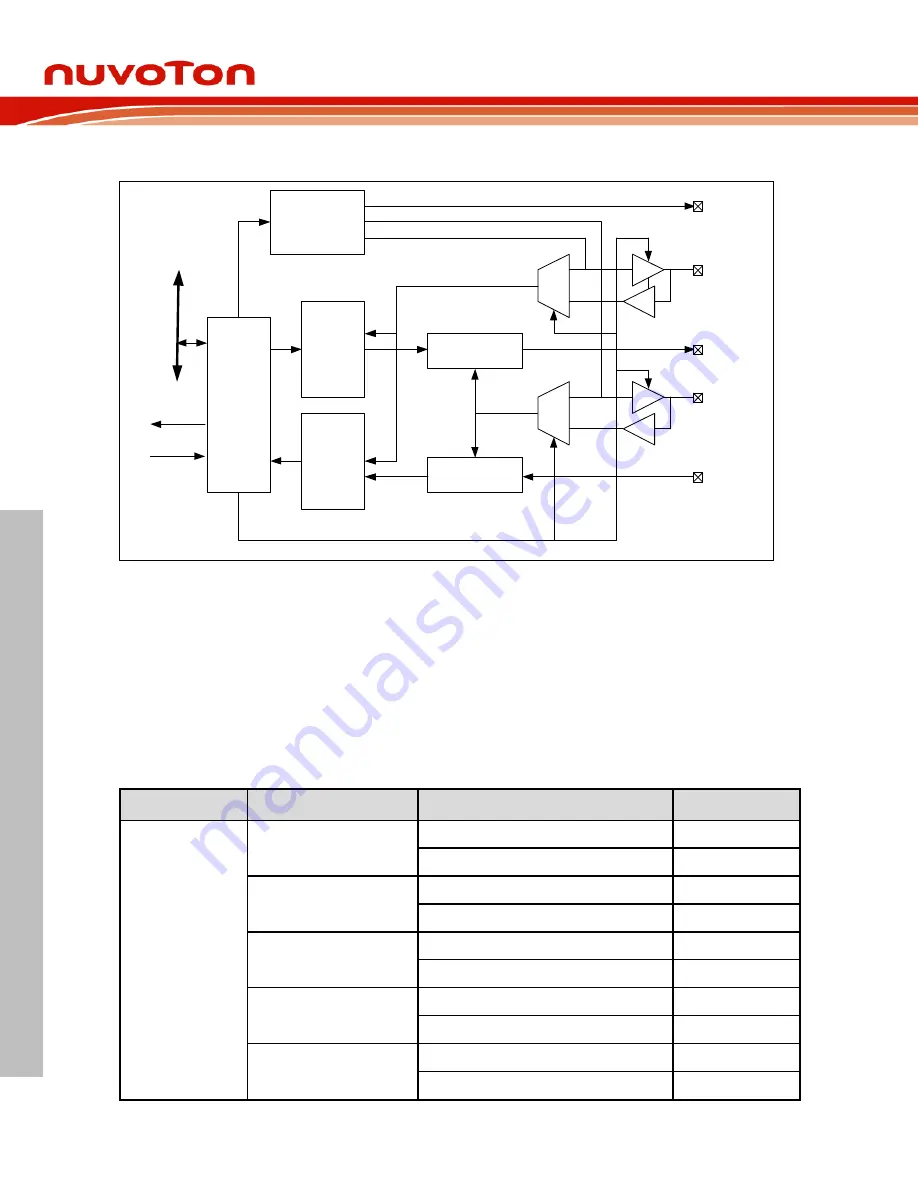

6.17.3 Block Diagram

Transmit

Contrl

&

TXFIFO

Receive

Control

&

RXFIFO

Tx Shift Register

Rx Shift Register

I2S Clock

Generator

Slave

MUX

MUX

APB Bus

Shift Clock

I2S_MCLK

I2S_LRCLK

I2S_DO

I2S_DI

I2S_BCLK

dma_req

dma_ack

APB

Interface

&

Control

Registers

Figure 6.17-1 I

2

S Controller Block Diagram

6.17.4 Basic Configuration

Clock source configuration

–

Select the source of I

2

S peripheral clock on I2SSEL (CLK_CLKSEL3[17:16]).

–

Enable I

2

S peripheral clock in I2SCKEN (CLK_APBCLK0[29]).

Reset configuration

–

Reset I

2

S controller in I2SRST (SYS_IPRST1[29]).

Pin configuration

Group

Pin Name

GPIO

MFP

I2S0

I2S0_BCLK

PD.0

MFP4

PD.6

MFP3

I2S0_DI

PB.13

MFP2

PD.4

MFP4

I2S0_DO

PB.14

MFP2

PD.5

MFP3

I2S0_LRCK

PD.1

MFP4

PD.3

MFP3

I2S0_MCLK

PB.15

MFP2

PD.2

MFP3