ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

141

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

1

0

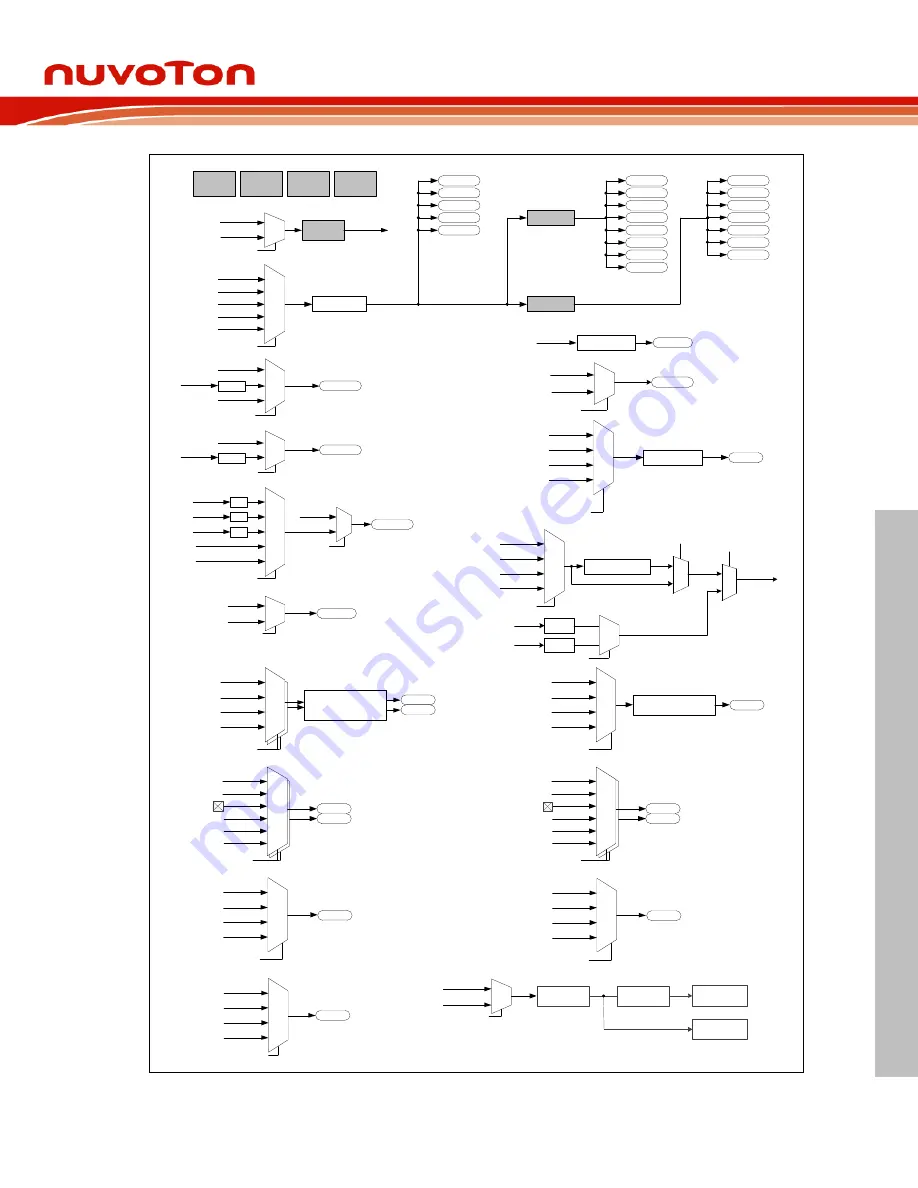

CLK_PLLCTL[19]

HIRC

48 / 49.152

MHz

HXT

4~24.576

MHz

PLL FOUT

111

011

010

001

HXT

LXT

HXT

HCLK

HIRC

000

1/2

1/2

1/2

CLK_CLKSEL0[5:3]

1

0

SysTick

RTC

WDT

CPU

LXT

32.768

kHz

LIRC

10

kHz

011

010

001

PLLFOUT

LXT

HXT

LIRC

000

CLK_CLKSEL0[2:0]

SYST_CTRL[2]

CPUCLK

1/(1)

LIRC

LIRC

11

10

CLK_CLKSEL1[1:0]

HCLK

1/2048

HIRC

HXT

01

LXT

111

HIRC

1

0

LXT

CLK_CLKSEL3[8]

EADC

1/(1)

PCLK1

WWDT

11

10

CLK_CLKSEL1[31:30]

HCLK

1/2048

/1,/2,/4,/8,/16

CRC

PCLK0

PLLFOUT

LIRC

CLK_CLKSEL1[29:28]

HCLK

HXT

HIRC

LXT

11

10

01

00

/2

(CLK_CLKOCTL[3:0]+1)

CLKO

0

1

DIV1EN

(CLK_CLKOCTL[5])

0

1

CLK1HZEN

(CLK_CLKOCTL[6])

1 Hz clock from RTC

LXT

LIRC

RTCSEL(CLK_CLKSEL3[8])

/10000

CLK_CLKSEL2[3:2]

CLK_CLKSEL2[7:6]

PCLK0

HXT

HIRC

PLLFOUT

11

10

01

00

1/(SPI0_CLKDIV[8:0]+1)

1/(SPI2_CLKDIV[8:0]+1)

SPI0

SPI2

CLK_CLKSEL2[5:4]

PCLK1

HXT

HIRC

PLLFOUT

11

10

01

00

1/(SPI1_CLKDIV[8:0]+1)

SPI1

PWM 0

1

0

PLLFOUT

PCLK0

CLK_CLKSEL2[0]

I2S

PCLK0

HXT

HIRC

PLLFOUT

CLK_CLKSEL3[17:16]

11

10

01

00

111

010

001

000

PCLK0

LXT

HXT

HIRC

CLK_CLKSEL1 [10:8]

CLK_CLKSEL1[14:12]

101

LIRC

011

TM0/TM1

TMR0

TMR1

111

010

001

000

PCLK1

LXT

HXT

HIRC

101

LIRC

011

TM2/TM3

TMR2

TMR3

CLK_CLKSEL1 [18:16]

CLK_CLKSEL1[22:20]

HCLK

PCLK1

/1,/2,/4,/8,/16

UART0

LXT

HXT

HIRC

PLLFOUT

CLK_CLKSEL1[25:24]

11

10

01

00

PWM0

EADC

I2C0

SPI0

SPI2

TMR0

TMR1

I2C1

RTC

SPI1

TMR2

TMR3

FMC

PDMA

SRAM

I2S

DPWM

1

0

/32768

CLK_CLKSEL2[11:10]

PCLK1

HXT

HIRC

PLLFOUT

11

10

01

00

DMIC

USB1.1 Device

Controller

USB1.1 PHY

/( 1)

/4

48MHz

1/(U1)

CLK_CLKSEL2[13:12]

PCLK0

HXT

HIRC

PLLFOUT

11

10

01

00

DPWM

DMIC

PLLFOUT

1

0

HIRC

CLK_CLKSEL4[24]

Figure 6.3-1 Clock Generator Global View Diagram