ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

143

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

6.3.3

System Clock and SysTick Clock

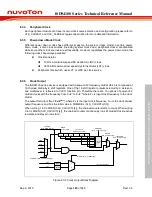

Five clock sources can be used to drive the system clock (HCLK), as shown in Figure 6.3-3. Clock

source can be chosen by configuring HCLKSEL bits(CLK_CLKSEL0[2:0]).

011

010

001

PLLFOUT

LXT

HXT

LIRC

HCLKSEL

(CLK_CLKSEL0[2:0])

HIRC

000

1/(1)

HCLKDIV

(CLK_CLKDIV0[3:0])

CPU in Power Down Mode

CPU

AHB

APB1

CPUCLK

HCLK

PCLK1

111

1/(1)

1/(1)

APB0

PCLK0

Figure 6.3-3 System Clock Block Diagram

There are two clock failure detectors monitoring HXT and LXT; each has its own enabling and

interrupt control.

If HXT failure detector is enabled, the HIRC clock will be also enabled automatically. The clock

controller will automatically switch the system clock (HCLK) source from HXT to HIRC if the

following conditions are met:

•

HCLK clock source was from HXT, or from PLLOUT and PLL source clock was from HXT,

•

HXT clock failure has been detected.

An HXT clock failure condition will set HXTFIF bit (CLK_CLKDSTS[0]) 1, and raise an HXT failure

interrupt if HXTFIEN (CLK_CLKDCTL[5]) is enabled.

To recover from HXT failure, user can first disable HXT, then enable HXT, and then check if the

HXT clock stable bit HXTSTB (CLK_STATUS[0]) is 1. HXTSTB bit being 1 means HXT is recovered

and enabled so that system clock source can be switched to HXT again.

The hardware procedure of HXT failure detection and system clock source auto switch to HIRC is

shown in the Figure 6.3-4.