ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

203

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

32-bit Read

The code snippet below show how to do 32-bit read:

FMC->ISPCMD = FMC_ISPCMD_READ;

// op code for 32-bit read is 0x00

FMC->ISPADDR = u32Addr;

// the flash memory address where read from

FMC->ISPTRG = FMC_ISPTRG_ISPGO_Msk;

// set ISPGO bit to start reading

while (FMC->ISPTRG & FMC_ISPTRG_ISPGO_Msk) ; // ISPGO bit ==1

operation in progress

return FMC->ISPDAT;

64-bit Read

Code snippet below show how to do 64-bit read:

FMC->ISPCMD = FMC_ISPCMD_READ_64;

// op code for 64-bit read is 0x40

FMC->ISPADDR = u32addr;

FMC->ISPDAT = 0x0;

FMC->ISPTRG = FMC_ISPTRG_ISPGO_Msk;

// set ISPGO bit to start reading

while (FMC->ISPSTS & FMC_ISPSTS_ISPBUSY_Msk) ;

…

*u32data0 = FMC->MPDAT0;

*u32data1 = FMC->MPDAT1;

6.4.4.5.2 Write Operations

The ISD94100 series supports 32-bit, 64-bit and multi-word flash write operations.

32-bit Write

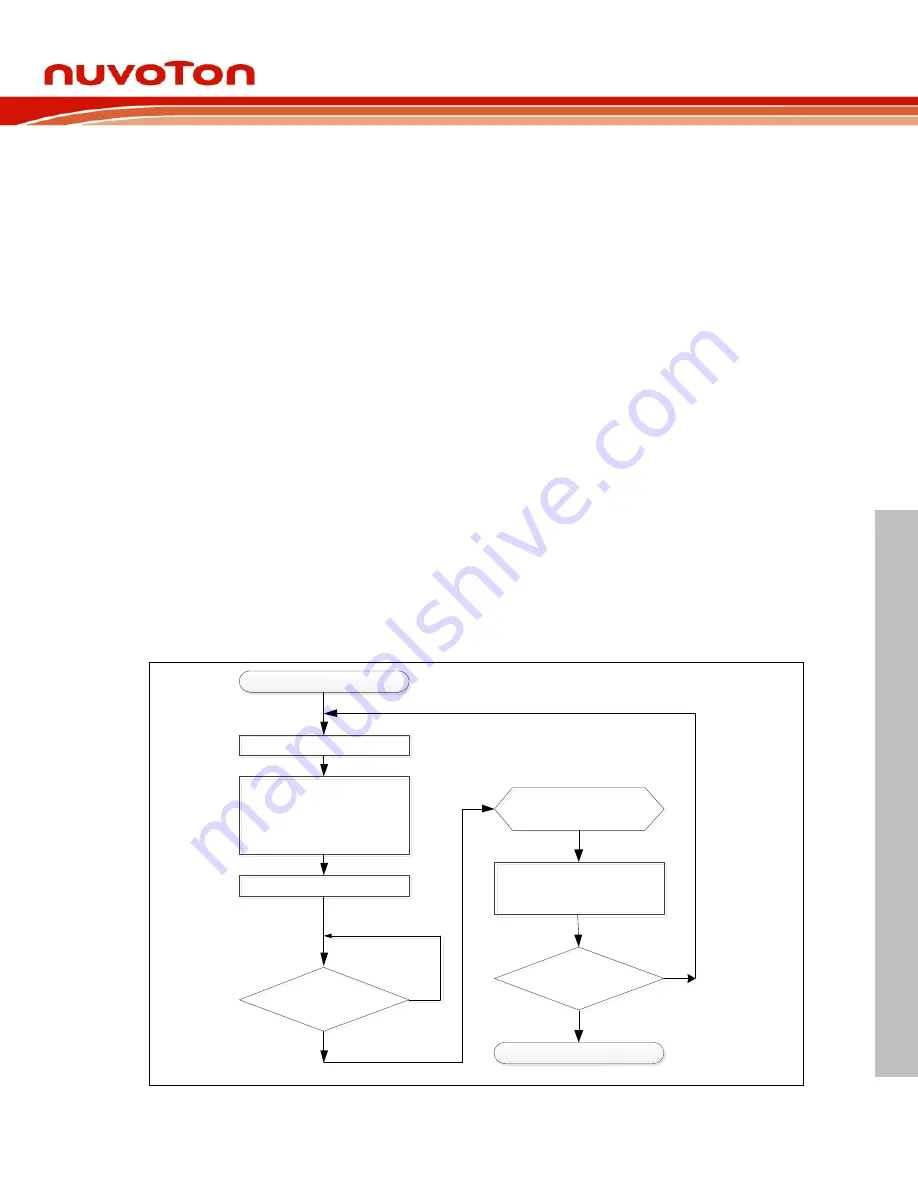

Figure 6.4-9 illustrates the operation flow of 32-bit write. The user first writes the 32-bit data into

FMC_ISPDAT register and in turn the device will write the data into the flash destination address.

Enable ISPEN

Set ISPGO = 1

End of ISP

Operation

?

Check ISPFF = 1?

YES

End of Flash Operation

NO

Set PT

Write FMC_ISPADDR

Write FMC_ISPCMD

Write FMC_ISPDAT

Check ISPGO = 0

?

NO

YES

Start

Stop

Figure 6.4-9 flash 32-bit write procedure