ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

353

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

6.7.6.6

PWM Counter Operation mode

The PWM counter supports two operation modes: one-shot mode and auto-reload mode. PWM

counter will operate in one-shot mode if CNTMODE (TIMERx_PWMCTL[3]) bit is set to 1, and

operate in auto-reload mode if CNTMODE bit is set to 0.

In both modes, CMP (TIMERx_PWMCMPDAT[15:0]) and PERIOD (TIMERx_PWMPERIOD[15:0])

should be written first and then set CNTEN (TIMERx_PWMCTL[0]) bit to 1 to start counter running.

In one-shot mode, PWM counter value will reload to default value according count type after one

PWM period is completed. User can write CMP to continuous one-shot operation to generate next

one-shot pulse once no matter current one-shot counter is running or completed.

In auto-reload mode, PWM counter is continuous running with current active PERIOD and CMP. If

user set PERIOD to zero in auto-reload mode, PWM counter value will reload to default value

according count type after one PWM period is completed.

6.7.6.7

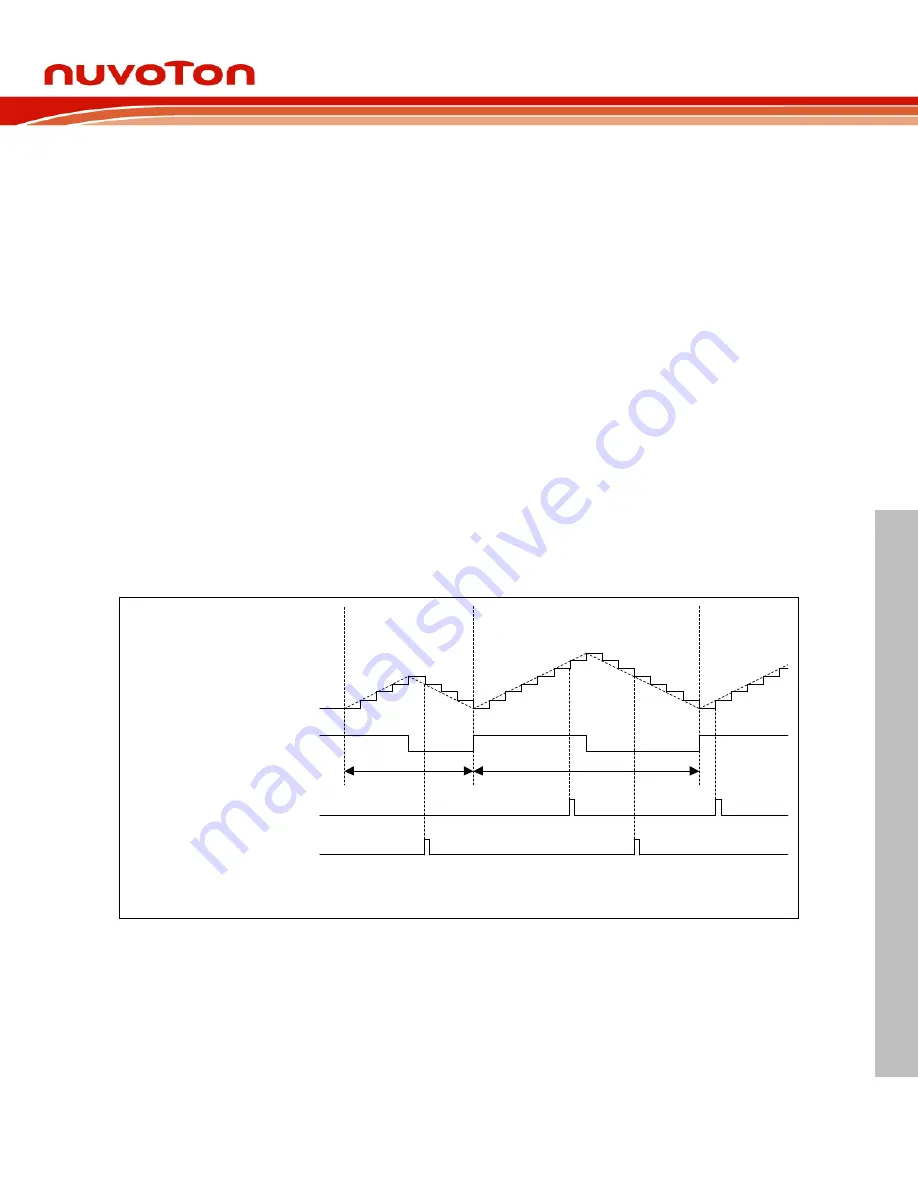

PWM Comparator

The CMP (TIMERx_PWMCMPDAT[15:0]) is comparator register of PWM. The CMP value is

continuously compared to the corresponding counter value. When the counter is equal to CMP,

PWM generates a compared point event. This event will generate PWM output pulse, interrupt

signal or trigger ADC start convert. In up-down count type, two events will be generated in a PWM

period as shown in Figure 6.7-17. The CMPU is up count compared point event and CMPD is down

count compared point event.

PWMDIRF

(TIMERx_PWMCNT[16])

0

1

2

3

4

3

1

2

0

1

2

3

4

3

1

2

0

5

6

7

6

4

5

1

2

3

4

PWM Period

PERIOD = 4

CMPDAT = 4

PERIOD = 7

CMPDAT = 5

PWM Period

Up-count compared

point event (CMPU)

Down-count compared

point event (CMPD)

PERIOD = 5

CMPDAT= 0

PWMCNT

(TIMERx_PWMCNT[15:0])

Note:

No CMPU event occurred when CMPDAT equals to PERIOD.

Figure 6.7-17 PWM Comparator Events in Up-Down Count Type

6.7.6.8

Period Loading Mode

When the IMMLDEN (TIMERx_PWMCTL[9]) bit set to 0, PWM operates at period loading mode.

The PWM provides PBUF (TIMERx_PWMPBUF[15:0]) is the active PERIOD buffer register and

CMPBUF (TIMERx_PWMCMPBUF[15:0]) is the active CMP buffer register. In period loading mode,

both PERIOD (TIMERx_PWMPERIOD[15:0]) and CMP (TIMERx_PWMCMPDAT[15:0]) will load to

their active PBUF and CMPBUF register while each PWM period is completed. Figure 6.7-18 shows

period loading timing of up count type, where PERIOD DATA0 denotes the initial data of PERIOD,