ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

408

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

PWM0_CH1

PB.1

MFP3

PB.3

MFP1

PB.5

MFP2

PWM0_CH2

PB.2

MFP3

PB.6

MFP2

PC.4

MFP1

PWM0_CH3

PB.3

MFP5

PB.7

MFP2

PC.13

MFP1

PD.12

MFP3

PWM0_CH4

PB.4

MFP5

PB.8

MFP2

PC.14

MFP1

PWM0_CH5

PB.9

MFP2

PD.7

MFP1

PWM0_SYNC_IN

PB.0

MFP1

PWM0_SYNC_OUT

PB.1

MFP1

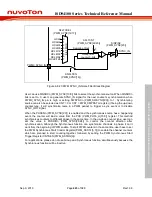

6.8.5

Functional Description

6.8.5.1

PWM Prescaler

PWM prescaler is used to divide clock source, prescaler counting 1 times, PWM counter

only count once. The pre-scale double buffer is setting by CLKPSC (PWM_CLKPSCn[11:0], n = 0,

2, 4) bits. Figure 6.8-6 is an example of PWM channel 0 prescale waveform. The prescale counter

will reload CLKPSC at the begin of the next prescale counter down-count.

0

1

CNT

(PWM_CNT0[15:0])

4

Prescale counter

CLKPSC

(PWM_CLKPSC0_1[11:0])

3 2 1 0

3

CNTEN0

(PWM_CNTEN[0])

4 3 2 1 0 4 3 2 1 0

5 4 3 2 1

6

0

0

2

4

6

PWM0_CLK

4

6

4 3 2 1 0

x

Figure 6.8-6 PWM0_CH0 Prescaler Waveform in Up Counter Type