ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

426

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

Dead Time

12-bits

Dead Time

12-bits

DTEN

(PWM_DTCTL0_1[16])

Independent Mode

Four Steps

Independent Mode

Four Steps

DTCNT

(PWM_DTCTL0_1[11:0])

Pulse

Generation

Complementary Mode

PWM0_CH0

PWM0_CH1

Dead Time Insertion Control

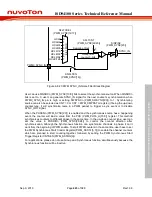

Figure 6.8-27 PWM0_CH0 and PWM0_CH1 Output Control in Complementary Mode

6.8.5.21 Dead-Time Insertion

In the complementary application, the complement channels may drive the external devices like

power switches. The dead-time generator inserts a low level period called “dead-time” between

complementary outputs to drive these devices safely and to prevent system or devices from the

burn-out damage. Hence the dead-time control is a crucial mechanism to the proper operation of

the complementary system. By setting corresponding channel n DTEN (PWM_DTCTLn_m[16]) bit

to enable dead-time function and DTCNT (PWM_DTCTLn_m[11:0]) to control dead-time period,

the dead-time can be calculated from the following formula:

Dead-time = (DTCNT (PWM_DTCTLn[11:0])+1) * PWM0_CLK period

Dead-time insertion clock source can be selected from prescaler output by setting DTCKSEL

(PWM_DTCTLn_m[24]) to 1. By default, clock source is come from PWM_CLK, which is prescaler

input. Then the dead-time can be calculated from the following formula:

Dead-time = (DTCNT (PWM_DTCTLn[11:0])+1) *

(CLKPSC (PWM_CLKPSCn [11:0])+1)*PWM0_CLK period

Please note that the PWM_DTCTLn_m are write-protected registers.

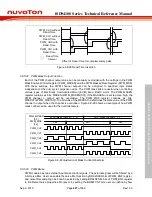

Figure 6.8-28 indicates the dead-time insertion for one pair of PWM signals.