ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

46

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

6

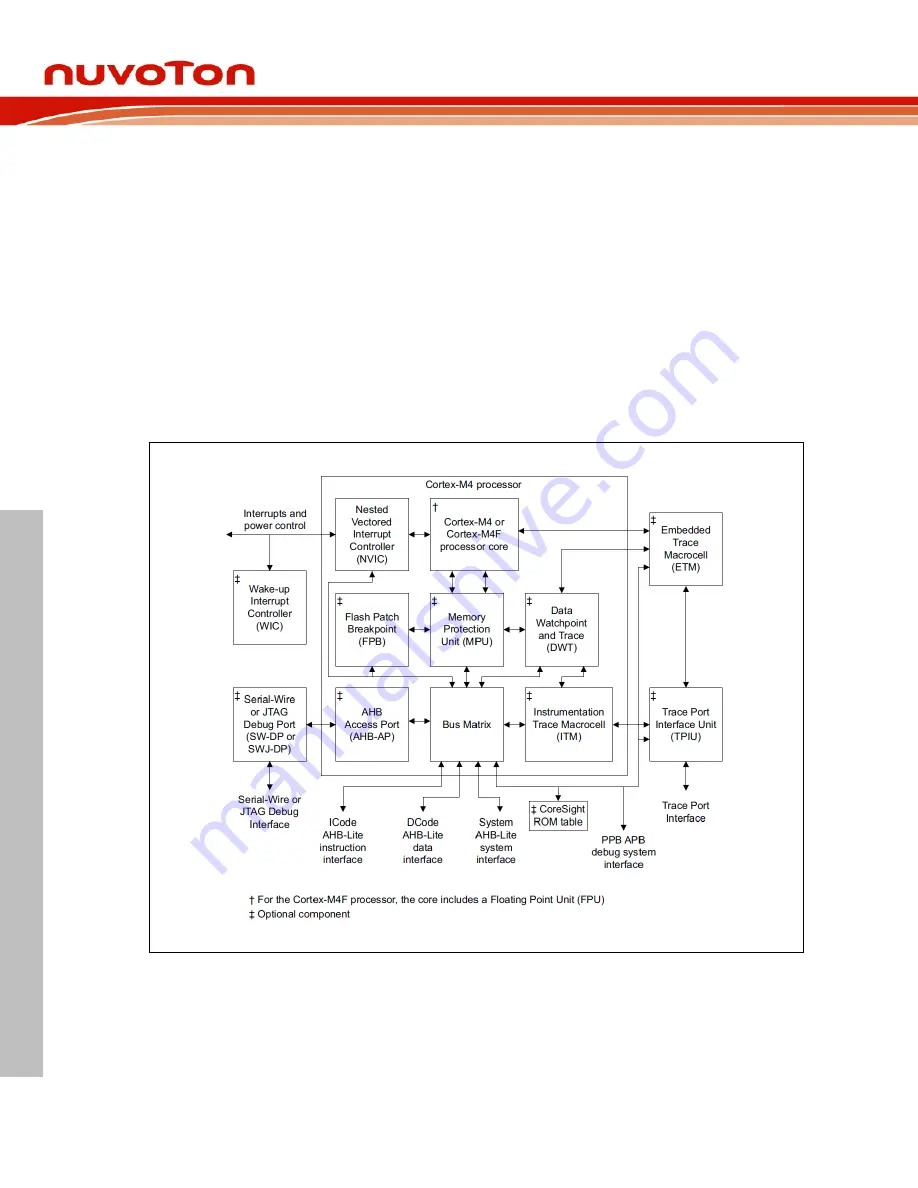

FUNCTIONAL DESCRIPTION

6.1

ARM

®

Cortex

®

-M4 Core

The Cortex

®

-M4 processor, a configurable, multistage, 32-bit RISC processor, has three AMBA

AHB-Lite interfaces for best parallel performance and includes an NVIC component. The processor

with optional hardware debug functionality can execute Thumb code and is compatible with other

Cortex

®

-M profile processors. The profile supports two modes -Thread mode and Handler mode.

Handler mode is entered as a result of an exception. An exception return can only be issued in

Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception

return. The Cortex

®

-M4F is a processor with the same capability as the Cortex

®

-M4 processor and

includes floating point arithmetic functionality. The ISD94100 series contains an embedded

Cortex

®

-M4F processor. Throughout this document, the name Cortex

®

-M4 refers to both Cortex

®

-

M4 and Cortex

®

-M4F processors. The following figure shows the functional controller of the

processor.

Figure 6.1-1 Cortex

®

-M4 Block Diagram

Cortex

®

-M4 processor features:

A low gate count processor core, with low latency interrupt processing that has:

A subset of the Thumb instruction set, defined in the

ARMv7-M Architecture

Reference Manual