ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

758

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

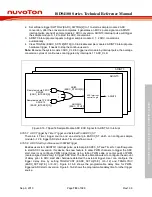

Disable hardware Trigger

19

to

1

MUX

TRGSEL(EADC_SCTL0[20:16])

EADC0_ST pin signal

ADC

Sample and

Priority

control

Logic

Sample

Module 0

Result

Register

DAT0

CHSEL

(EADC_SCTL0[3:0])

ADINT0 interrupt EOC pulse

ADINT1 interrupt EOC pulse

Sample Module

0

Sample Module

3

TRGDLYDIV (EADC_SCTL0[7:6])

SWTRG0~3 Software

trigger

0h

1h

Fh

8-bit Up

Counter

TRGDLYCNT

(EADC_SCTL0[15:8])

/1, /2, /4, /16

ADC_CLK

=

reset

EOC0

reset pulse

Eh

9h

5h

2h

3h

Ah

Bh

Ch

Dh

EOC0

Timer0 overflow pulse

4h

Timer1 overflow pulse

Timer2 overflow pulse

Timer3 overflow pulse

6h

7h

8h

10h

11h

12h

13h

PWM0TG0

PWM0TG1

PWM0TG2

PWM0TG3

PWM0TG4

PWM0TG5

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Double

Data

Register

DDAT0

EXTREN (EADC_SCTL0[4])

EXTFEN (EADC_SCTL0[5])

14h

15h

Reserved

Reserved

Figure 6.16-2 Sample Module 0~3 Block Diagram