ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

867

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

–

The DMIC module is reset by DMICRST (SYS_IPRST1[15]).

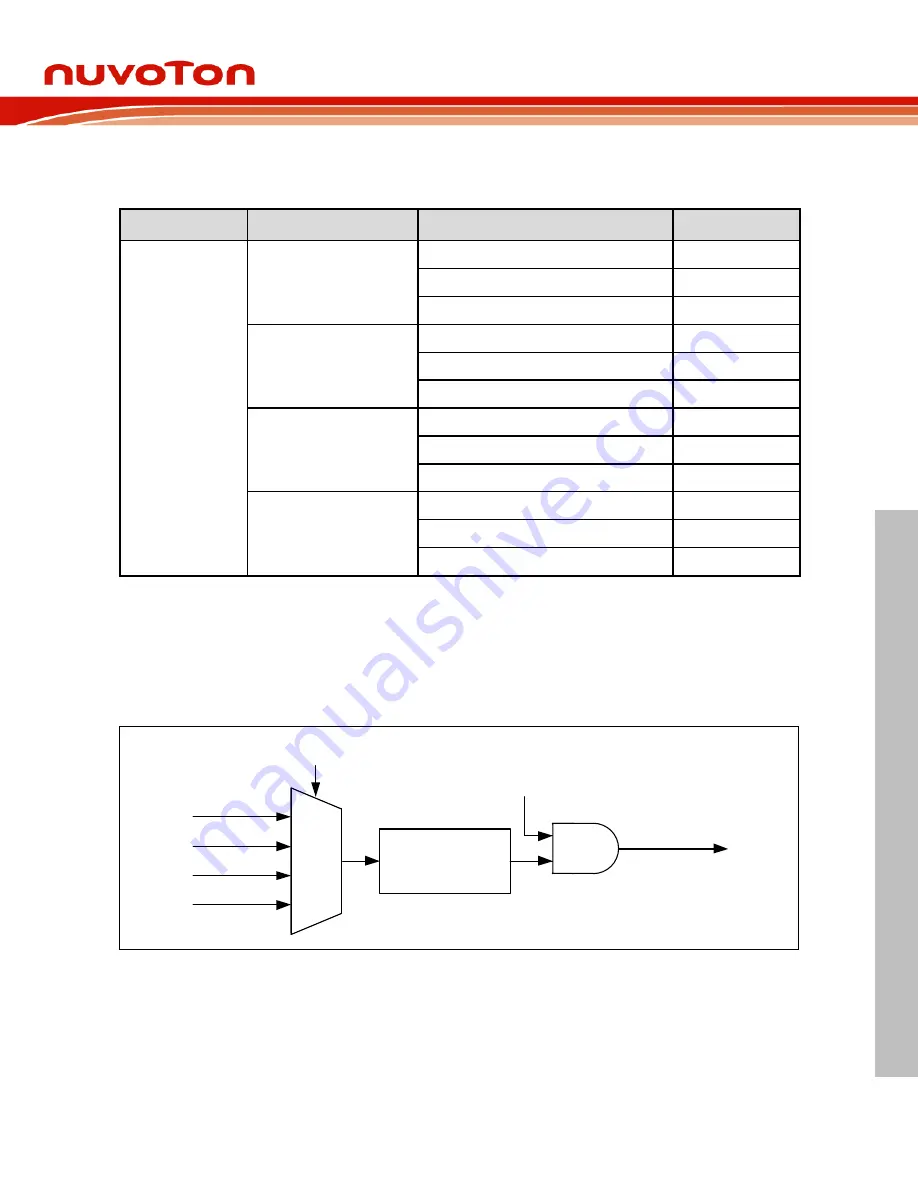

Pin configuration

Group

Pin Name

GPIO

MFP

DMIC

DMIC_DAT0

PA.0

MFP3

PB.5

MFP5

PD.6

MFP4

DMIC_CLK0

PA.1

MFP3

PB.6

MFP5

PD.5

MFP4

DMIC_DAT1

PA.2

MFP3

PB.3

MFP3

PD.4

MFP4

DMIC_CLK1

PA.3

MFP3

PB.4

MFP3

PD.3

MFP4

6.19.5 Functional Description

6.19.5.1 DMIC Woking Main Clock Generator

The DMIC module has four clock sources selected by DMICSEL (CLK_CLKSEL2[11:10]). The

frequency of the DMIC working main clock (DMIC_MCLK) must be less than 30MHz. The DMIC

clock control diagram is shown in Figure 6.19-2.

11

10

01

00

PCLK1

PLL FOUT

HXT

HIRC

PCLKDIV = DMIC_DIV[7:0]

1/(1)

DMICCKEN (CLK_APBCLK0 [15])

DMICSEL (CLK_CLKSEL2 [11:10])

DMIC_MCLK

Figure 6.19-2 DMIC Clock Control Diagram

6.19.5.2 DMIC Bus Clock Generator

To generate DMIC bus clock (DMIC_CLK) based on DMIC working main clock (DMIC_MCLK)

F_DMIC_CLK = F_DMIC_MCLK/(1 + MCLKDIV).

Where F_DMIC_CLK is the frequency of DMIC_CLK and F_DMIC_MCLK is the frequency of