ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

880

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

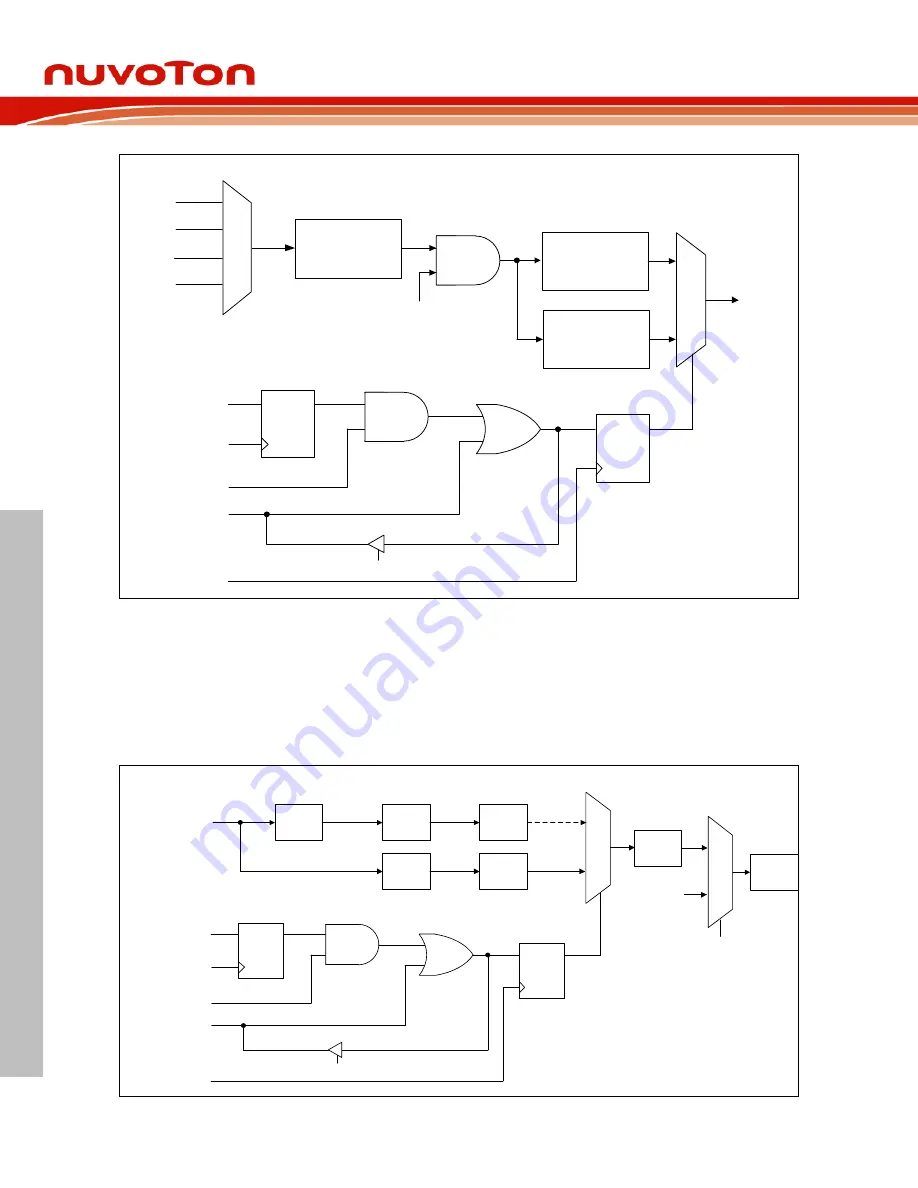

1/(1+PCLKDIV)

HIRC

PCLK1

PLLFOUT

HXT

DMICCKEN

(CLK_APBCLK0[15])

11

10

01

00

1/(1+MCLKDIV)

1/4

1

0

CHEN0

(DMIC_CTL[0])

Note:

PCLKDIV = DMIC_DIV[7:0]

MCLKDIV = DMIC_DIV[15:8]

DMIC_MCLK

DMIC Path

(DMIC_CLK)

VAD Path

(VAD_CLK)

DMIC_CLK

D

Q

D

Q

ACTCL (VAD_SINCCTL[30])

ACTIVE

(VAD_STATUS0[31])

ACTCL

(VAD_SINCCTL[30])

VADEN

(VAD_SINCCTL[31])

SW

(VAD_SINCCTL[29])

Figure 6.20-2 VAD Clock Control Diagram

6.20.5.2 VAD Data Control

The VAD data diagram is shown in Figure 6.20-3.

When VAD enabled (VADEN (VAD_SINCCTL[31]) = 1) and voice detected (ACTIVE

(VAD_STATUS0[31]) = 1), the PCM data can be sent to SRAM via PDMA to do key word detection

by software solution. And user can stop sending PCM data to SRAM by setting register DATAOFF

(VAD_SINCCTL[28]).

SINC

Biquad

VAD

[15:0]

SINC

DMIC

[23:0]

1

0

FIFO

0

1

X

DMIC_IN (CH0)

PDMA

VAD Path

DMIC Path

DATAOFF

(VAD_SINCCTL[28])

Note:

X: Data output always be 0

CHEN0

(DMIC_CTL[0])

D

Q

D

Q

ACTCL (VAD_SINCCTL[30])

ACTIVE

(VAD_STATUS0[31])

ACTCL

(VAD_SINCCTL[30])

VADEN

(VAD_SINCCTL[31])

SW

(VAD_SINCCTL[29])