ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

897

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

6.21 Audio DPWM Modulator (DPWM)

6.21.1 Overview

The DPWM modulator is sigma-delta modulator which is for class D amplifer. ISD94100 series has

3 DPWM modulator and each one can provide 2 differential pins.

6.21.2 Features

Differential Audio PWM Output (DPWM)

Support left channel,right channel and sub-woofer channel.

Support sample rates from 16~96kHz.

Programeable biquad filter with 10 band

PDMA data channel for streaming of PCM audio data.

Support the single precision floating point for input data and BIQ coefficient

Provides one 32-level FIFO data buffers for transmitting.

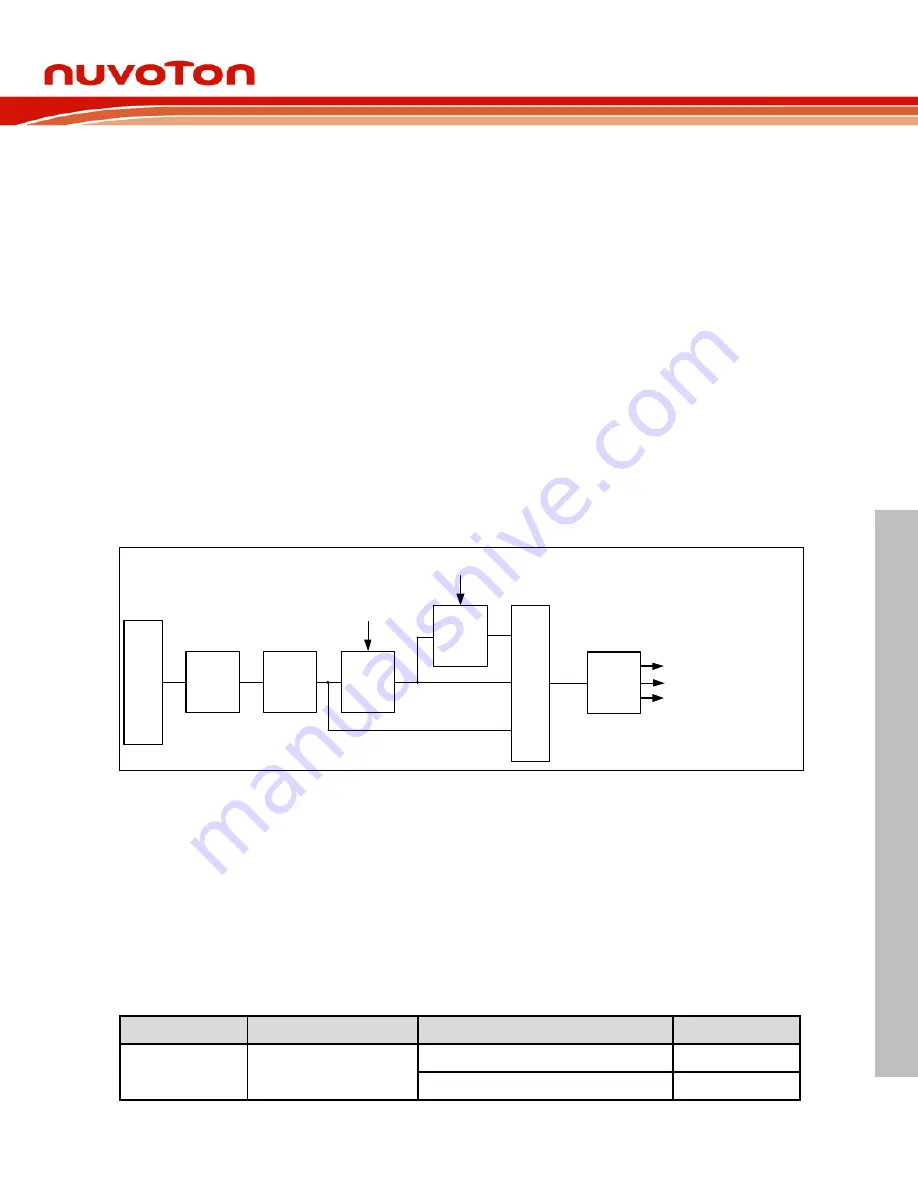

6.21.3 Block Diagram

APB

AFIFO

FltToFix

BIQ

6band

Spliter

BIQ 4band

SEL

2.0

2.0

2.0

2.0

2.0

2.0

2.1

2.0/2.1

DPWM_LP/DPWM_LN pin

DPWM_RP/DPWM_RN pin

DPWM_SP/DPWM_SN pin

Programmable Coefficient

Programmable Coefficient

DPWM

Modulator

Figure 6.21-1 DPWM Block Diagram

6.21.4 Basic Configuration

Clock source configuration

–

The source of DPWM peripheral clock is selected by DPWMSEL

(CLK_CLKSEL2[13:12]).

–

The DPWM peripheral clock is enabled by DPWMCKEN (CLK_APBCLK1[6]).

Reset configuration

–

The DPWM module is reset by DPWMRST (SYS_IPRST2[6]).

Pin configuration

Group

Pin Name

GPIO

MFP

DPWM

DPWM_LN

PA.4

MFP3

PC.12

MFP3